www.ti.com SBOS489 – DECEMBER 2011

## **Sournd**TM Low-Power, Low Noise and Distortion, Bipolar-Input AUDIO OPERATIONAL AMPLIFIERS

Check for Samples: OPA1662, OPA1664

#### **FEATURES**

Low Noise: 3.3 nV/√Hz at 1 kHz

Low Distortion: 0.00006% at 1 kHz

Low Quiescent Current:

1.5 mA per Channel

Slew Rate: 17 V/µs

Wide Gain Bandwidth: 22 MHz (G = +1)

Unity Gain StableRail-to-Rail OutputWide Supply Range:

±1.5 V to ±18 V, or +3 V to +36 V

Dual and Quad Versions Available

Small Package Sizes:

Dual: SO-8 and MSOP-8

Quad: SO-14 and TSSOP-14

#### **APPLICATIONS**

- USB and Firewire Audio Systems

- Analog and Digital Mixers

- Portable Recording Systems

- Audio Effects Processors

- High-End A/V Receivers

- High-End DVD and Blu-Ray™ Players

- HIGH-End Car Audio

#### DESCRIPTION

The OPA1662 (dual) and OPA1664 (quad) series of bipolar-input operational amplifiers achieve a low 3.3 nV/ $\sqrt{\text{Hz}}$  noise density with an ultralow distortion of 0.00006% at 1 kHz. The OPA1662 and OPA1664 series of op amps offer rail-to-rail output swing to within 600 mV with 2-k $\Omega$  load, which increases headroom and maximizes dynamic range. These devices also have a high output drive capability of  $\pm 30$  mA.

These devices operate over a very wide supply range of ±1.5 V to ±18 V, or +3 V to +36 V, on only 1.5 mA of supply current per channel. The OPA1662 and OPA1664 op amps are unity-gain stable and provide excellent dynamic behavior over a wide range of load conditions.

These devices also feature completely independent circuitry for lowest crosstalk and freedom from interactions between channels, even when overdriven or overloaded.

The OPA1662 and OPA1664 are specified from -40°C to +85°C.

A

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

SoundPlus is a trademark of Texas Instruments Incorporated. Blu-Ray is a trademark of Blu-Ray Disc Association. All other trademarks are the property of their respective owners. SBOS489 – DECEMBER 2011 www.ti.com

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

#### PACKAGE INFORMATION(1)

| PRODUCT | PACKAGE-LEAD | PACKAGE DESIGNATOR | PACKAGE MARKING |

|---------|--------------|--------------------|-----------------|

| OD44662 | SO-8         | D                  | OP1662          |

| OPA1662 | MSOP-8       | DGK                | OUQI            |

| OD44664 | SO-14        | D                  | OP1664          |

| OPA1664 | TSSOP-14     | PW                 | OP1664          |

<sup>(1)</sup> For the most current package and ordering information see the Package Option Addendum at the end of this document, or visit the device product folder at <a href="https://www.ti.com">www.ti.com</a>.

#### **ABSOLUTE MAXIMUM RATINGS**(1)

Over operating free-air temperature range (unless otherwise noted).

|                    |                                                         | OPA1662, OPA1664           | UNIT       |  |  |  |

|--------------------|---------------------------------------------------------|----------------------------|------------|--|--|--|

| Supply voltage, V  | $V_{S} = (V+) - (V-)$                                   | 40                         | V          |  |  |  |

| Input voltage      |                                                         | (V-) - 0.5 to $(V+) + 0.5$ | V          |  |  |  |

| Input current (all | nput current (all pins except power-supply pins) ±10 mA |                            |            |  |  |  |

| Output short-circu | uit <sup>(2)</sup>                                      | Continuo                   | Continuous |  |  |  |

| Operating temper   | rature range                                            | -55 to +125                | °C         |  |  |  |

| Storage temperat   | ture range                                              | -65 to +150                | °C         |  |  |  |

| Junction tempera   | ture                                                    | 200                        | °C         |  |  |  |

|                    | Human body model (HBM)                                  | 2                          | kV         |  |  |  |

| ESD ratings        | Charged device model (CDM)                              | 1                          | kV         |  |  |  |

|                    | Machine model (MM)                                      | 200                        | V          |  |  |  |

<sup>(1)</sup> Stresses above these ratings may cause permanent damage. Exposure to absolute maximum conditions for extended periods may degrade device reliability. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those specified is not supported.

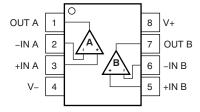

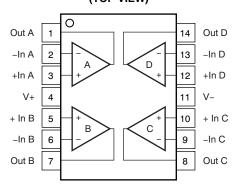

#### **PIN CONFIGURATIONS**

#### OPA1662: D AND DGK PACKAGES SO-8 AND MSOP-8 (TOP VIEW)

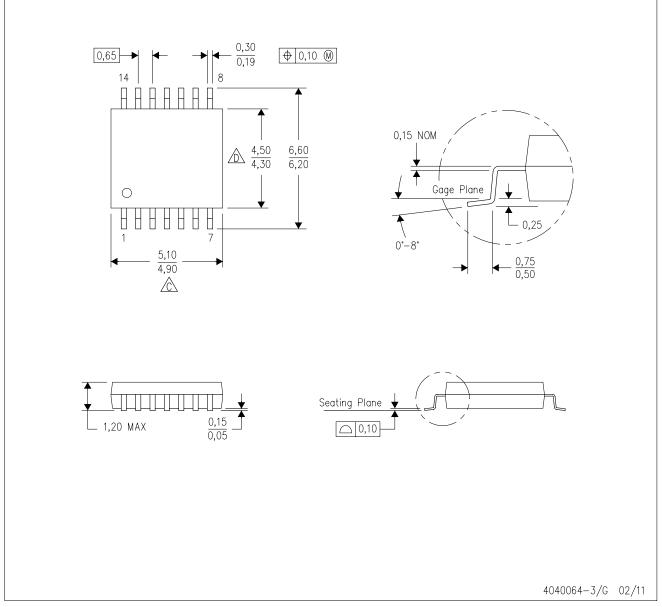

#### OPA1664: D AND PW PACKAGES SO-14 AND TSSOP-14 (TOP VIEW)

<sup>(2)</sup> Short-circuit to V<sub>S</sub>/2 (ground in symmetrical dual supply setups), one amplifier per package.

www.ti.com SBOS489 - DECEMBER 2011

#### ELECTRICAL CHARACTERISTICS: $V_S = \pm 15 \text{ V}$

At  $T_A = +25^{\circ}C$  and  $R_L = 2 \text{ k}\Omega$ , unless otherwise noted.  $V_{CM} = V_{OUT} = \text{midsupply}$ , unless otherwise noted.

|                          | +25 C and $R_L = 2 \text{ k}\Omega$ , unless                     |                                | OW OOT TT                                                           |            | 62, OPA1664      |            |                    |

|--------------------------|------------------------------------------------------------------|--------------------------------|---------------------------------------------------------------------|------------|------------------|------------|--------------------|

|                          | PARAMETER                                                        |                                | CONDITIONS                                                          | MIN        | TYP              | MAX        | UNIT               |

| AUDIO I                  | PERFORMANCE                                                      |                                |                                                                     |            |                  |            |                    |

|                          |                                                                  |                                |                                                                     |            | 0.00006          |            | %                  |

| THD+N                    | Total harmonic distortion + noise                                | G = +1, f = 1 k                | $Hz$ , $V_O = 3 V_{RMS}$                                            |            | -124             |            | dB                 |

|                          |                                                                  |                                | SMPTE/DIN two-tone, 4:1                                             |            | 0.00004          |            | %                  |

|                          |                                                                  |                                | (60 Hz and 7 kHz)                                                   |            | -128             |            | dB                 |

|                          |                                                                  | G = +1,                        | DIM 30                                                              |            | 0.00004          |            | %                  |

| IMD                      | Intermodulation distortion                                       | $V_O = 3 V_{RMS}$              | (3-kHz square wave and 15-kHz sine wave)                            |            | -128             |            | dB                 |

|                          |                                                                  |                                | CCIF twin-tone                                                      |            | 0.00004          |            | %                  |

|                          |                                                                  |                                | (19 kHz and 20 kHz)                                                 |            | -128             |            | dB                 |

| FREQUI                   | ENCY RESPONSE                                                    |                                |                                                                     |            |                  |            |                    |

| GBW                      | Gain-bandwidth product                                           | G = +1                         |                                                                     |            | 22               |            | MHz                |

| SR                       | Slew rate                                                        | G = -1                         |                                                                     |            | 17               |            | V/µs               |

|                          | Full power bandwidth <sup>(1)</sup>                              | $V_O = 1 V_P$                  |                                                                     |            | 2.7              |            | MHz                |

|                          | Overload recovery time                                           | G = -10                        |                                                                     |            | 1                |            | μs                 |

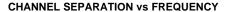

|                          | Channel separation (dual and quad)                               | f = 1 kHz                      |                                                                     |            | -120             |            | dB                 |

| NOISE                    |                                                                  |                                |                                                                     |            |                  |            |                    |

| e <sub>n</sub>           | Input voltage noise                                              | f = 20 Hz to 20                | ) kHz                                                               |            | 2.8              |            | $\mu V_{PP}$       |

|                          | Input voltage noise density                                      | f = 1 kHz                      |                                                                     |            | 3.3              |            | nV/√ <del>Hz</del> |

|                          | input voltage fields defield                                     | f = 100 Hz                     |                                                                     |            | 5                |            | nV/√Hz             |

| I <sub>n</sub>           | Input current noise density                                      | f = 1 kHz                      |                                                                     |            | 1                |            | pA/√Hz             |

|                          | · · · · · · · · · · · · · · · · · · ·                            | f = 100 Hz                     |                                                                     |            | 2                |            | pA/√Hz             |

| OFFSET                   | VOLTAGE                                                          |                                |                                                                     |            |                  |            |                    |

| Vos                      | Input offset voltage                                             | $V_{S} = \pm 1.5 \text{ V to}$ |                                                                     |            | ±0.5             | ±1.5       | mV                 |

|                          |                                                                  |                                | $\pm 18 \text{ V}, T_A = -40^{\circ}\text{C to } +85^{\circ}^{(2)}$ |            | 2                | 8          | μV/°C              |

| PSRR                     | Power-supply rejection ratio                                     | $V_{S} = \pm 1.5 \text{ V to}$ | ±18 V                                                               |            | 1                | 3          | μV/V               |

|                          | BIAS CURRENT                                                     |                                |                                                                     |            |                  |            |                    |

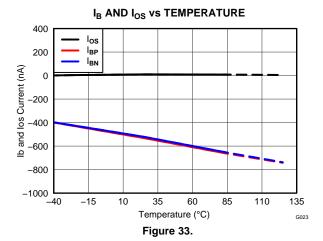

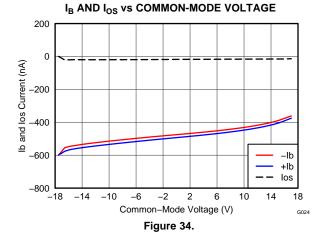

| I <sub>B</sub>           | Input bias current                                               | $V_{CM} = 0 V$                 |                                                                     |            | 600              | 1200       | nA                 |

| los                      | Input offset current                                             | $V_{CM} = 0 V$                 |                                                                     |            | ±25              | ±100       | nA                 |

|                          | OLTAGE RANGE                                                     | T                              |                                                                     |            |                  |            |                    |

| V <sub>CM</sub>          | Common-mode voltage range                                        |                                |                                                                     | (V-) +0.5  |                  | (V+) – 1   | V                  |

| CMRR                     | Common-mode rejection ratio                                      |                                |                                                                     | 106        | 114              |            | dB                 |

| INPUT                    | MPEDANCE                                                         |                                |                                                                     |            | 470 !! 0         |            | 10    5            |

|                          | Differential                                                     |                                |                                                                     |            | 170    2         |            | kΩ    pF           |

| ODENI                    | Common-mode OOP GAIN                                             |                                |                                                                     |            | 600    2.5       |            | MΩ    pF           |

|                          |                                                                  | (\/ \ \ \ 0.6.\/ <             | $V_0 \le (V+) - 0.6 \text{ V}, R_L = 2 \text{ k}\Omega$             | 106        | 114              |            | dB                 |

| A <sub>OL</sub><br>OUTPU | Open-loop voltage gain                                           | (v-) + U.0 V ≤                 | $v_0 = (v+) - 0.0 \text{ V}, R_L = 2 \text{ K}\Omega$               | 100        | 114              |            | UD                 |

|                          | Output voltage                                                   | $R_L = 2 k\Omega$              |                                                                     | (V-) + 0.6 |                  | (V+) - 0.6 | V                  |

| V <sub>OUT</sub>         | Output voltage  Output current                                   | INL = 2 K12                    |                                                                     | , ,        | al Characteristi | . ,        | mA                 |

| l <sub>OUT</sub>         | •                                                                |                                |                                                                     |            |                  |            |                    |

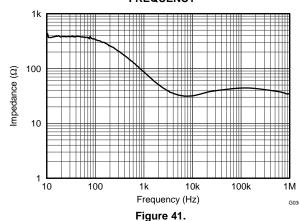

| Z <sub>O</sub>           | Open-loop output impedance  Short-circuit current <sup>(3)</sup> |                                |                                                                     | See Typica | al Characteristi | <u> </u>   | Ω                  |

| l <sub>sc</sub>          |                                                                  |                                |                                                                     |            | ±50              |            | mA<br>~F           |

| C <sub>LOAD</sub>        | Capacitive load drive                                            |                                |                                                                     |            | 200              |            | pF                 |

<sup>(1)</sup> Full-power bandwidth =  $SR/(2\pi \times V_P)$ , where SR = slew rate. (2) Specified by design and characterization.

One channel at a time.

SBOS489 - DECEMBER 2011 www.ti.com

#### ELECTRICAL CHARACTERISTICS: $V_S = \pm 15 \text{ V}$ (continued)

At  $T_A = +25^{\circ}C$  and  $R_L = 2 \text{ k}\Omega$ , unless otherwise noted.  $V_{CM} = V_{OUT} = \text{midsupply}$ , unless otherwise noted.

|      |                         |                                                                          | OPA16 | OPA1662, OPA1664 |      |      |  |

|------|-------------------------|--------------------------------------------------------------------------|-------|------------------|------|------|--|

|      | PARAMETER               | CONDITIONS                                                               | MIN   | TYP              | MAX  | UNIT |  |

| POWI | ER SUPPLY               |                                                                          |       |                  |      |      |  |

| Vs   | Specified voltage range |                                                                          | ±1.5  |                  | ±18  | V    |  |

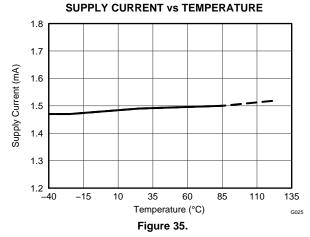

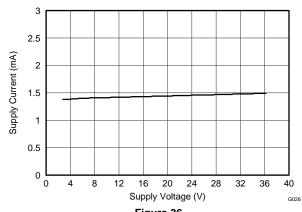

|      | Quiescent current       | I <sub>OUT</sub> = 0 A                                                   |       | 1.5              | 1.8  | mA   |  |

| IQ   | (per channel)           | $I_{OUT} = 0 \text{ A}, T_A = -40^{\circ}\text{C to } +85^{\circ}^{(4)}$ |       |                  | 2    | mA   |  |

| TEMP | PERATURE                | •                                                                        |       |                  |      |      |  |

|      | Specified range         |                                                                          | -40   |                  | +85  | °C   |  |

|      | Operating range         |                                                                          | -55   |                  | +125 | °C   |  |

<sup>(4)</sup> Specified by design and characterization.

#### **ELECTRICAL CHARACTERISTICS:** V<sub>S</sub> = +5 V

At  $T_A = +25^{\circ}C$  and  $R_L = 2 \text{ k}\Omega$ , unless otherwise noted.  $V_{CM} = V_{OUT} = \text{midsupply}$ , unless otherwise noted.

|                  |                                     |                                |                                                                       | OPA16     | OPA1662, OPA1664 |          |                    |

|------------------|-------------------------------------|--------------------------------|-----------------------------------------------------------------------|-----------|------------------|----------|--------------------|

|                  | PARAMETER                           |                                | CONDITIONS                                                            | MIN       | TYP              | MAX      | UNIT               |

| AUDIO I          | PERFORMANCE                         | •                              |                                                                       | •         |                  |          |                    |

| THD+N            | Total harmonic distortion + noise   | G _ +1 f _ 1 l                 | $Hz$ , $V_O = 3 V_{RMS}$                                              |           | 0.0001           |          | %                  |

| I HD+N           | Total Harmonic distortion + noise   | G = +1, 1 = 1 F                | $mz$ , $v_0 = 3 v_{RMS}$                                              |           | -120             |          | dB                 |

|                  |                                     |                                | SMPTE/DIN two-tone, 4:1                                               |           | 0.00004          |          | %                  |

|                  |                                     |                                | (60 Hz and 7 kHz)                                                     |           | -128             |          | dB                 |

| 11.45            | Intermodulation distortion          | G = +1,                        | DIM 30                                                                |           | 0.00004          |          | %                  |

| IMD              |                                     | $V_0 = 3 V_{RMS}$              | (3-kHz square wave and 15-kHz sine wave)                              |           | -128             |          | dB                 |

| 1                |                                     |                                | CCIF twin-tone                                                        |           | 0.00004          |          | %                  |

|                  |                                     |                                | (19 kHz and 20 kHz)                                                   |           | -128             |          | dB                 |

| FREQUI           | ENCY RESPONSE                       |                                | +                                                                     |           |                  |          |                    |

| GBW              | Gain-bandwidth product              | G = +1                         |                                                                       |           | 20               |          | MHz                |

| SR               | Slew rate                           | G = -1                         |                                                                       |           | 13               |          | V/µs               |

|                  | Full power bandwidth <sup>(1)</sup> | $V_O = 1 V_P$                  |                                                                       |           | 2                |          | MHz                |

|                  | Overload recovery time              | G = -10                        |                                                                       |           | 1                |          | μs                 |

|                  | Channel separation (dual and quad)  | f = 1 kHz                      |                                                                       |           | -120             |          | dB                 |

| NOISE            |                                     | •                              |                                                                       |           |                  | Ÿ        |                    |

| $\mathbf{e}_{n}$ | Input voltage noise                 | f = 20 Hz to 20                | ) kHz                                                                 |           | 3.3              |          | $\mu V_{PP}$       |

|                  | Input voltage noise density         | f = 1 kHz                      |                                                                       |           | 3.3              |          | nV/√ <del>Hz</del> |

|                  | input voltage noise density         | f = 100 Hz                     |                                                                       |           | 5                |          | nV/√ <del>Hz</del> |

| I <sub>n</sub>   | Input current noise density         | f = 1 kHz                      |                                                                       |           | 1                |          | pA/√ <del>Hz</del> |

| 'n               | input current noise density         | f = 100 Hz                     |                                                                       |           | 2                |          | pA/√ <del>Hz</del> |

| OFFSET           | VOLTAGE                             |                                |                                                                       |           |                  |          |                    |

| Vos              | Input offset voltage                | $V_{S} = \pm 1.5 \text{ V to}$ |                                                                       |           | ±0.5             | ±1.5     | mV                 |

| *05              | mpat onoct voltage                  | $V_S = \pm 1.5 \ V \ to$       | $\pm 18 \text{ V}, T_A = -40^{\circ}\text{C to } +85^{\circ}{}^{(2)}$ |           | 2                | 8        | μV/°C              |

| PSRR             | Power-supply rejection ratio        | $V_S = \pm 1.5 \text{ V to}$   | ±18 V                                                                 |           | 1                | 3        | μV/V               |

| INPUT E          | BIAS CURRENT                        |                                |                                                                       |           |                  |          |                    |

| I <sub>B</sub>   | Input bias current                  | $V_{CM} = 0 V$                 |                                                                       |           | 600              | 1200     | nA                 |

| I <sub>OS</sub>  | Input offset current                | $V_{CM} = 0 V$                 |                                                                       |           | ±25              | ±100     | nA                 |

| INPUT V          | OLTAGE RANGE                        |                                |                                                                       |           |                  |          |                    |

| V <sub>CM</sub>  | Common-mode voltage range           |                                |                                                                       | (V-) +0.5 |                  | (V+) – 1 | V                  |

| CMRR             | Common-mode rejection ratio         |                                |                                                                       | 86        | 100              |          | dB                 |

| INPUT I          | MPEDANCE                            |                                |                                                                       |           |                  | T        |                    |

|                  | Differential                        |                                |                                                                       |           | 170    2         |          | kΩ    pF           |

|                  | Common-mode                         |                                |                                                                       |           | 600    2.5       |          | MΩ    pF           |

Full-power bandwidth = SR/( $2\pi \times V_P$ ), where SR = slew rate. Specified by design and characterization.

<sup>(2)</sup>

www.ti.com SBOS489 – DECEMBER 2011

#### **ELECTRICAL CHARACTERISTICS:** V<sub>S</sub> = +5 V (continued)

At  $T_A = +25^{\circ}C$  and  $R_L = 2 \text{ k}\Omega$ , unless otherwise noted.  $V_{CM} = V_{OUT} = \text{midsupply}$ , unless otherwise noted.

|                   |                                      |                                                                                  | OPA16      | 62, OPA1664       |           |      |

|-------------------|--------------------------------------|----------------------------------------------------------------------------------|------------|-------------------|-----------|------|

|                   | PARAMETER                            | CONDITIONS                                                                       | MIN        | TYP               | MAX       | UNIT |

| OPEN-I            | LOOP GAIN                            |                                                                                  |            |                   |           |      |

| A <sub>OL</sub>   | Open-loop voltage gain               | $(V-) + 0.6 \text{ V} \le V_0 \le (V+) - 0.6 \text{ V}, R_L = 2 \text{ k}\Omega$ | 90         | 100               |           | dB   |

| OUTPU             | т                                    |                                                                                  |            |                   |           |      |

| V <sub>OUT</sub>  | Output voltage                       | $R_L = 2 k\Omega$                                                                | (V-) + 0.6 | (                 | V+) - 0.6 | V    |

| I <sub>OUT</sub>  | Output current                       |                                                                                  | See Typic  | I Characteristics |           | mA   |

| Z <sub>O</sub>    | Open-loop output impedance           |                                                                                  | See Typic  | al Characteristi  | CS        | Ω    |

| I <sub>SC</sub>   | Short-circuit current <sup>(3)</sup> |                                                                                  |            | ±40               |           | mA   |

| C <sub>LOAD</sub> | Capacitive load drive                |                                                                                  |            | 200               |           | pF   |

| POWER             | R SUPPLY                             |                                                                                  |            |                   |           |      |

| Vs                | Specified voltage range              |                                                                                  | ±1.5       |                   | ±18       | V    |

|                   | Quiescent current                    | I <sub>OUT</sub> = 0 A                                                           |            | 1.4               | 1.7       | mA   |

| IQ                | (per channel)                        | $I_{OUT} = 0 \text{ A}, T_A = -40^{\circ}\text{C to } +85^{\circ}^{(2)}$         |            |                   | 2         | mA   |

| TEMPE             | RATURE                               |                                                                                  |            |                   |           |      |

|                   | Specified range                      |                                                                                  | -40        |                   | +85       | °C   |

|                   | Operating range                      |                                                                                  | -55        |                   | +125      | °C   |

<sup>(3)</sup> One channel at a time.

#### **THERMAL INFORMATION: OPA1662**

|                                              | OP                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| THERMAL METRIC <sup>(1)</sup>                | D (SO)                                                                                                                                                                                                            | DGK (MSOP)                                                                                                                                                                                                                                                                                | UNITS                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|                                              | 8 PINS                                                                                                                                                                                                            | 8 PINS                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| Junction-to-ambient thermal resistance       | 156.3                                                                                                                                                                                                             | 225.4                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| Junction-to-case (top) thermal resistance    | 85.5                                                                                                                                                                                                              | 78.8                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| Junction-to-board thermal resistance         | 64.9                                                                                                                                                                                                              | 110.5                                                                                                                                                                                                                                                                                     | 9044                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| Junction-to-top characterization parameter   | 33.8                                                                                                                                                                                                              | 14.6                                                                                                                                                                                                                                                                                      | °C/W                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| Junction-to-board characterization parameter | 64.3                                                                                                                                                                                                              | 108.5                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| Junction-to-case (bottom) thermal resistance | N/A                                                                                                                                                                                                               | N/A                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

|                                              | Junction-to-ambient thermal resistance  Junction-to-case (top) thermal resistance  Junction-to-board thermal resistance  Junction-to-top characterization parameter  Junction-to-board characterization parameter | THERMAL METRIC <sup>(1)</sup> D (SO)  8 PINS  Junction-to-ambient thermal resistance 156.3  Junction-to-case (top) thermal resistance 85.5  Junction-to-board thermal resistance 64.9  Junction-to-top characterization parameter 33.8  Junction-to-board characterization parameter 64.3 | 8 PINS         8 PINS           Junction-to-ambient thermal resistance         156.3         225.4           Junction-to-case (top) thermal resistance         85.5         78.8           Junction-to-board thermal resistance         64.9         110.5           Junction-to-top characterization parameter         33.8         14.6           Junction-to-board characterization parameter         64.3         108.5 |  |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

#### **THERMAL INFORMATION:OPA1664**

|                  |                                              | OPA1664 |            |       |  |  |

|------------------|----------------------------------------------|---------|------------|-------|--|--|

|                  | THERMAL METRIC <sup>(1)</sup>                | D (SO)  | PW (TSSOP) | UNITS |  |  |

|                  |                                              | 14 PINS | 14 PINS    |       |  |  |

| $\theta_{JA}$    | Junction-to-ambient thermal resistance       | 78.6    | 125.8      |       |  |  |

| $\theta_{JCtop}$ | Junction-to-case (top) thermal resistance    | 37.0    | 45.2       |       |  |  |

| $\theta_{JB}$    | Junction-to-board thermal resistance         | 24.9    | 57.5       | °C/W  |  |  |

| ΨЈТ              | Junction-to-top characterization parameter   | 9.7     | 5.5        | C/VV  |  |  |

| ΨЈВ              | Junction-to-board characterization parameter | 24.6    | 56.7       |       |  |  |

| $\theta_{JCbot}$ | Junction-to-case (bottom) thermal resistance | N/A     | N/A        |       |  |  |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

SBOS489 – DECEMBER 2011 www.ti.com

#### **TYPICAL CHARACTERISTICS**

At  $T_A$  = +25°C,  $V_S$  = ±15 V, and  $R_L$  = 2 k $\Omega$ , unless otherwise noted.

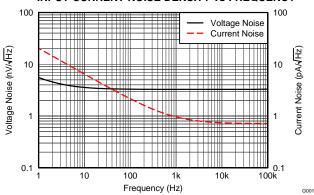

## INPUT VOLTAGE NOISE DENSITY AND INPUT CURRENT NOISE DENSITY vs FREQUENCY

Figure 1.

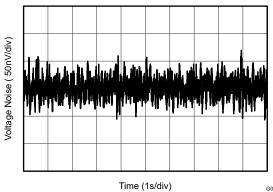

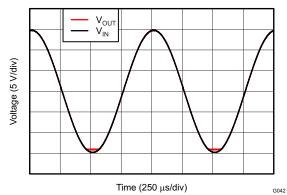

#### 0.1Hz TO 10Hz NOISE

**NSTRUMENTS**

Figure 2.

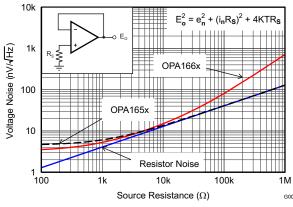

#### **VOLTAGE NOISE vs SOURCE RESISTANCE**

Figure 3.

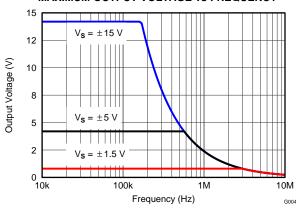

#### MAXIMUM OUTPUT VOLTAGE vs FREQUENCY

Figure 4.

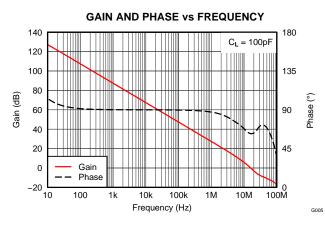

Figure 5.

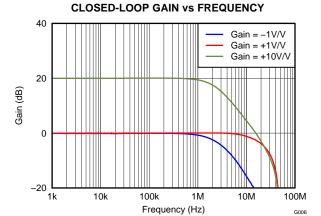

Figure 6.

#### **TYPICAL CHARACTERISTICS (continued)**

At  $T_A = +25$ °C,  $V_S = \pm 15$  V, and  $R_L = 2$  k $\Omega$ , unless otherwise noted.

INSTRUMENTS

#### TEXAS INSTRUMENTS

www.ti.com

#### TYPICAL CHARACTERISTICS (continued)

CMKK, PSKK (dB)

At  $T_A = +25$ °C,  $V_S = \pm 15$  V, and  $R_L = 2$  k $\Omega$ , unless otherwise noted.

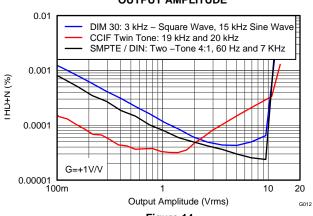

#### INTERMODULATION DISTORTION vs OUTPUT AMPLITUDE

Figure 14.

Figure 15.

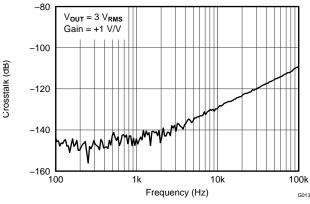

#### CMRR AND PSRR vs FREQUENCY (Referred to Input)

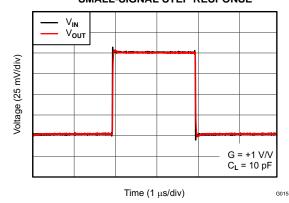

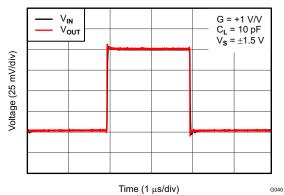

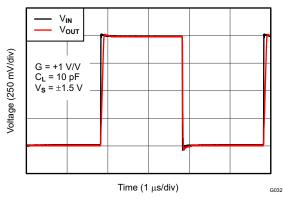

SMALL-SIGNAL STEP RESPONSE

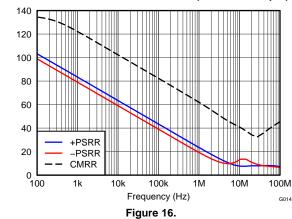

Figure 17.

**SMALL-SIGNAL STEP RESPONSE**

Figure 18.

#### **TYPICAL CHARACTERISTICS (continued)**

At  $T_A = +25$ °C,  $V_S = \pm 15$  V, and  $R_L = 2$  k $\Omega$ , unless otherwise noted.

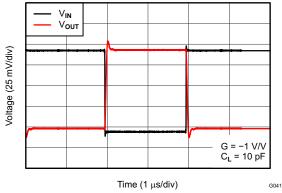

#### **SMALL-SIGNAL STEP RESPONSE**

Figure 19.

#### **SMALL-SIGNAL STEP RESPONSE**

Figure 20.

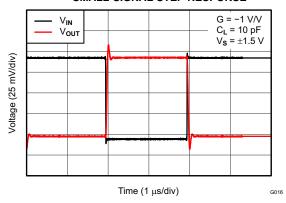

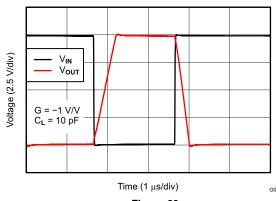

#### LARGE-SIGNAL STEP RESPONSE

Figure 21.

#### LARGE-SIGNAL STEP RESPONSE

Figure 22.

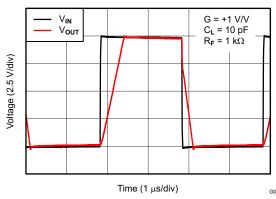

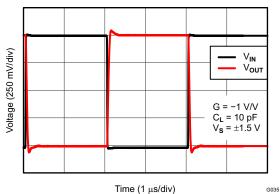

#### LARGE-SIGNAL STEP RESPONSE

Figure 23.

#### LARGE-SIGNAL STEP RESPONSE

Figure 24.

50

45

40

35

30

25

20 15

10

5

0

0

50

100

Overshoot (%)

SBOS489 - DECEMBER 2011

www.ti.com

#### TYPICAL CHARACTERISTICS (continued)

At  $T_A$  = +25°C,  $V_S$  = ±15 V, and  $R_L$  = 2 k $\Omega$ , unless otherwise noted.

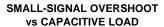

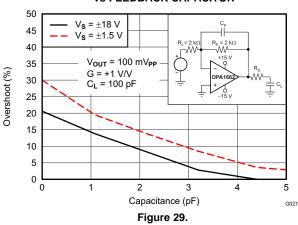

# SMALL-SIGNAL OVERSHOOT VS CAPACITIVE LOAD VOUT = $100 \text{ mV}_{PP}$ G = +1 V/V $R_S = 0 \Omega$

150 200 250 300 350 400

Capacitance (pF)

$R_s = 25 \Omega$

$R_s = 50 \Omega$

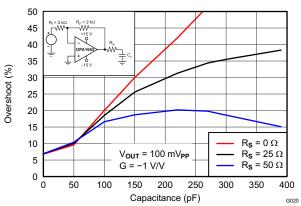

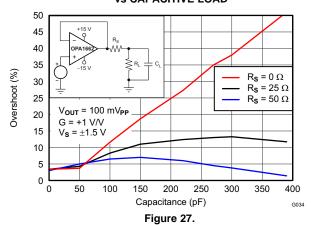

SMALL-SIGNAL OVERSHOOT vs CAPACITIVE LOAD

Figure 26.

Figure 25.

SMALL-SIGNAL OVERSHOOT vs CAPACITIVE LOAD

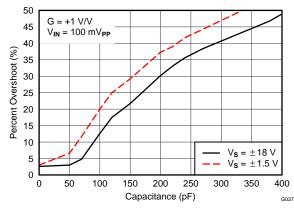

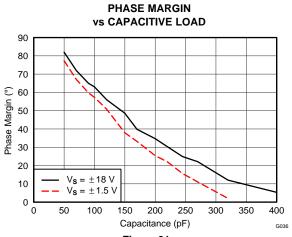

PERCENT OVERSHOOT vs CAPACITIVE LOAD

Figure 30.

#### **TYPICAL CHARACTERISTICS (continued)**

At  $T_A = +25$ °C,  $V_S = \pm 15$  V, and  $R_L = 2$  k $\Omega$ , unless otherwise noted.

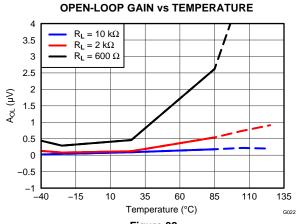

Figure 31.

Figure 32.

SUPPLY CURRENT vs SUPPLY VOLTAGE

Figure 36.

SBOS489 – DECEMBER 2011 www.ti.com

#### **TYPICAL CHARACTERISTICS (continued)**

At  $T_A$  = +25°C,  $V_S$  = ±15 V, and  $R_L$  = 2 k $\Omega$ , unless otherwise noted.

#### SHORT-CIRCUIT CURRENT vs TEMPERATURE 60 55 Short Circuit Current (mA) 50 45 40 35 +lsc -Isc 30 -15 60 110 Temperature (°C) G027

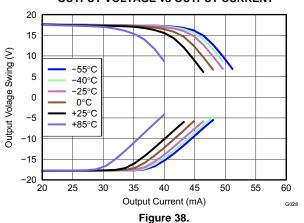

**OUTPUT VOLTAGE vs OUTPUT CURRENT**

**ISTRUMENTS**

Figure 37.

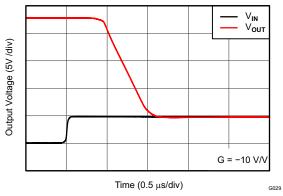

**POSITIVE OVERLOAD RECOVERY**

Figure 39.

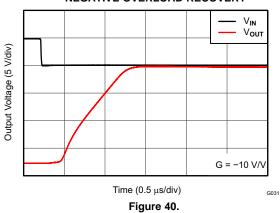

**NEGATIVE OVERLOAD RECOVERY**

OPEN-LOOP OUTPUT IMPEDANCE vs FREQUENCY

**NO PHASE REVERSAL**

Figure 42.

www.ti.com SBOS489 – DECEMBER 2011

#### APPLICATION INFORMATION

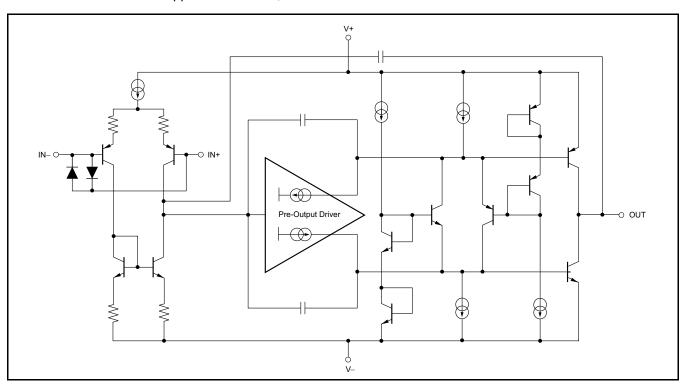

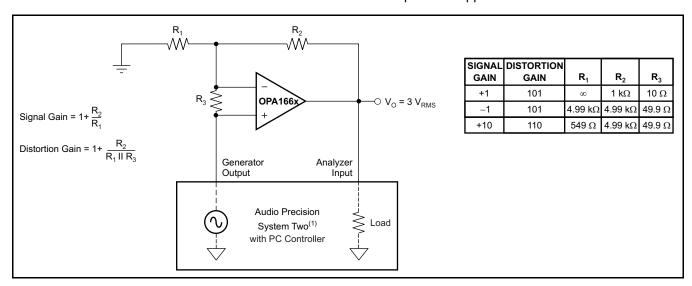

The OPA1662 and OPA1664 are unity-gain stable, precision dual and quad op amps with very low noise. Applications with noisy or high-impedance power supplies require decoupling capacitors close to the device pins. In most cases, 0.1-µF capacitors are adequate. Figure 43 shows a simplified schematic of the OPA166x (one channel shown).

#### **OPERATING VOLTAGE**

The OPA166x series op amps operate from ±1.5 V to ±18 V supplies while maintaining excellent performance. The OPA166x series can operate with as little as +3 V between the supplies and with up to +36 V between the supplies. However, some

applications do not require equal positive and negative output voltage swing. With the OPA166x series, power-supply voltages do not need to be equal. For example, the positive supply could be set to +25 V with the negative supply at -5 V.

In all cases, the common-mode voltage must be maintained within the specified range. In addition, key parameters are assured over the specified temperature range of  $T_A = -40^{\circ}\text{C}$  to +85°C. Parameters that vary significantly with operating voltage or temperature are shown in the Typical Characteristics.

Figure 43. OPA166x Simplified Schematic

SBOS489 – DECEMBER 2011 www.ti.com

#### INPUT PROTECTION

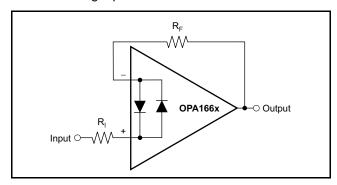

The input terminals of the OPA1662 and OPA1664 are protected from excessive differential voltage with back-to-back diodes, as Figure 44 illustrates. In most circuit applications, the input protection circuitry has no consequence. However, in low-gain or G = +1circuits, fast ramping input signals can forward bias these diodes because the output of the amplifier cannot respond rapidly enough to the input ramp. If the input signal is fast enough to create this forward bias condition, the input signal current must be limited to 10 mA or less. If the input signal current is not inherently limited, an input series resistor (R<sub>I</sub>) and/or a feedback resistor (R<sub>F</sub>) can be used to limit the signal input current. This resistor degrades the low-noise performance of the OPA166x and is examined in the following *Noise Performance* section. Figure 44 shows an example configuration when both current-limiting input and feeback resistors are used.

Figure 44. Pulsed Operation

#### **NOISE PERFORMANCE**

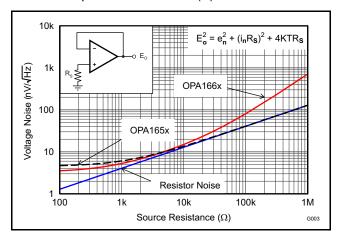

Figure 45 shows the total circuit noise for varying source impedances with the op amp in a unity-gain configuration (no feedback resistor network, and therefore no additional noise contributions).

The OPA166x (GBW = 22 MHz, G = +1) is shown with total circuit noise calculated. The op amp itself contributes both a voltage noise component and a current noise component. The voltage noise is commonly modeled as a time-varying component of the offset voltage. The current noise is modeled as the time-varying component of the input bias current and reacts with the source resistance to create a voltage component of noise. Therefore, the lowest noise op amp for a given application depends on the source impedance. For low source impedance, current noise is negligible, and voltage noise generally dominates. The low voltage noise of the OPA166x series op amps makes them a better choice for low source impedances of less than 1 k $\Omega$ .

The equation in Figure 45 shows the calculation of the total circuit noise, with these parameters:

**NSTRUMENTS**

- e<sub>n</sub> = Voltage noise

- i<sub>n</sub> = Current noise

- R<sub>S</sub> = Source impedance

- k = Boltzmann's constant = 1.38 × 10<sup>-23</sup> J/K

- T = Temperature in Kelvins (K)

Figure 45. Noise Performance of the OPA166x in Unity-Gain Buffer Configuration

#### **BASIC NOISE CALCULATIONS**

Design of low-noise op amp circuits requires careful consideration of a variety of possible noise contributors: noise from the signal source, noise generated in the op amp, and noise from the feedback network resistors. The total noise of the circuit is the root-sum-square combination of all noise components.

The resistive portion of the source impedance produces thermal noise proportional to the square root of the resistance. Figure 45 plots this equation. The source impedance is usually fixed; consequently, select the op amp and the feedback resistors to minimize the respective contributions to the total noise.

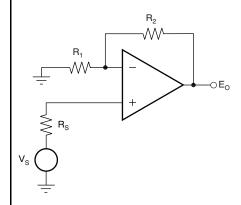

Figure 46 illustrates both inverting and noninverting op amp circuit configurations with gain. In circuit configurations with gain, the feedback network resistors also contribute noise. The current noise of the op amp reacts with the feedback resistors to create additional noise components. The feedback resistor values can generally be chosen to make these noise sources negligible. The equations for total noise are shown for both configurations.

#### A) Noise in Noninverting Gain Configuration

Noise at the output:

$$E_0^2 = \left(1 + \frac{R_2}{R_1}\right)^2 e_n^2 + \left(\frac{R_2}{R_1}\right)^2 e_1^2 + e_2^2 + \left(1 + \frac{R_2}{R_1}\right)^2 e_s^2$$

Where

$$e_S = \sqrt{4kTR_S}$$

= thermal noise of  $R_S$

$e_1 = \sqrt{4kTR_1}$  = thermal noise of  $R_1$

$e_2 = \sqrt{4kTR_2}$  = thermal noise of  $R_2$

B) Noise in Inverting Gain Configuration

Noise at the output:

$$E_{O}^{2} = \left[1 + \frac{R_{2}}{R_{1} + R_{S}}\right]^{2} e_{n}^{2} + \left[\frac{R_{2}}{R_{1} + R_{S}}\right]^{2} e_{1}^{2} + e_{2}^{2} + \left[\frac{R_{2}}{R_{1} + R_{S}}\right]^{2} e_{s}^{2}$$

Where

$$e_S = \sqrt{4kTR_S}$$

= thermal noise of  $R_S$

$e_1 = \sqrt{4kTR_1}$  = thermal noise of  $R_1$

$e_2 = \sqrt{4kTR_2}$  = thermal noise of  $R_2$

Note: For the OPA166x series of op amps at 1 kHz,  $e_n = 3.3 \text{ nV}/\sqrt{\text{Hz}}$ .

Figure 46. Noise Calculation in Gain Configurations

SBOS489 – DECEMBER 2011 www.ti.com

## TOTAL HARMONIC DISTORTION MEASUREMENTS

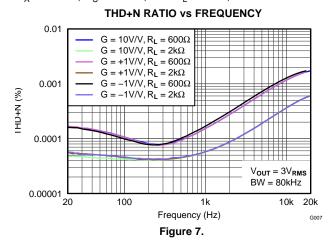

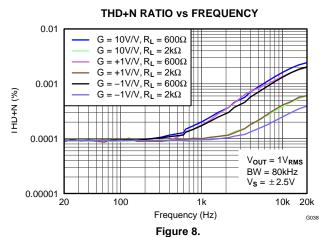

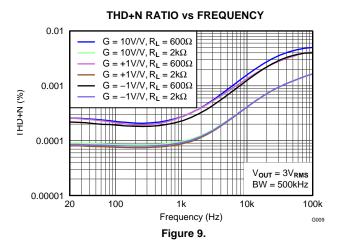

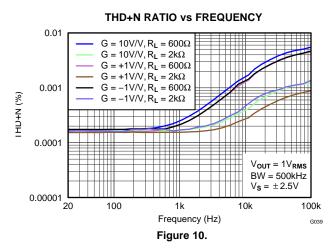

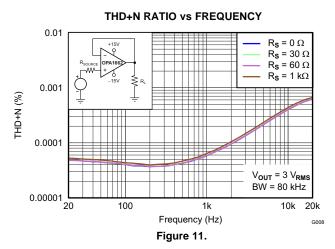

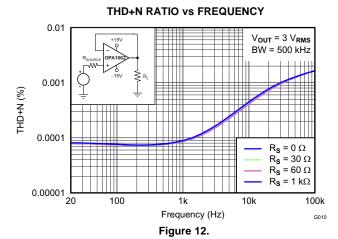

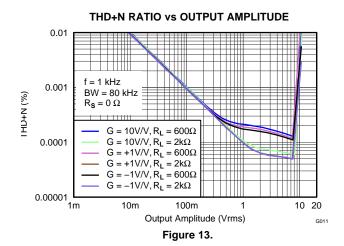

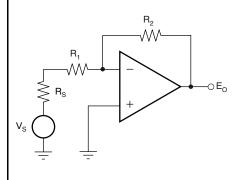

The OPA166x series op amps have excellent distortion characteristics. THD + noise is below 0.0006% (G = +1,  $V_O$  = 3  $V_{RMS}$ , BW = 80kHz) throughout the audio frequency range, 20 Hz to 20 kHz, with a 2-k $\Omega$  load (see Figure 7 for characteristic performance).

The distortion produced by the OPA166x series op amps is below the measurement limit of many commercially available distortion analyzers. However, a special test circuit (such as Figure 47 shows) can be used to extend the measurement capabilities.

Op amp distortion can be considered an internal error source that can be referred to the input. Figure 47 shows a circuit that causes the op amp distortion to be gained up (refer to the table in Figure 47 for the distortion gain factor for various signal gains). The addition of  $R_3$  to the otherwise standard noninverting amplifier configuration alters the feedback factor or noise gain of the circuit. The closed-loop gain is unchanged, but the feedback available for error correction is reduced by the distortion gain factor, thus extending the resolution by the same amount. Note that the input signal and load applied to the op amp are the same as with conventional feedback without  $R_3$ . The value of  $R_3$  should be kept small to minimize its effect on the distortion measurements.

The validity of this technique can be verified by duplicating measurements at high gain and/or high frequency where the distortion is within the measurement capability of the test equipment. Measurements for this data sheet were made with an Audio Precision System Two distortion/noise analyzer, which greatly simplifies such repetitive measurements. The measurement technique can, however, be performed with manual distortion measurement instruments.

#### CAPACITIVE LOADS

The dynamic characteristics of the OPA1662 and OPA1664 have been optimized for commonly encountered gains, loads, and operating conditions. The combination of low closed-loop gain and high capacitive loads decreases the phase margin of the amplifier and can lead to gain peaking or oscillations. As a result, heavier capacitive loads must be isolated from the output. The simplest way to achieve this isolation is to add a small resistor ( $R_{\rm S}$  equal to 50  $\Omega$ , for example) in series with the output.

This small series resistor also prevents excess power dissipation if the output of the device becomes shorted. Figure 25 illustrates a graph of *Small-Signal Overshoot vs Capacitive Load* for several values of R<sub>S</sub>. Also, refer to Applications Bulletin AB-028 (literature number SBOA015, available for download from the TI web site) for details of analysis techniques and application circuits.

(1) For measurement bandwidth, see Figure 7 through Figure 12.

Figure 47. Distortion Test Circuit

www.ti.com SBOS489 – DECEMBER 2011

#### POWER DISSIPATION

The OPA1662 and OPA1664 series op amps are capable of driving  $2\text{-}k\Omega$  loads with a power-supply voltage up to  $\pm 18$  V and full operating temperature range. Internal power dissipation increases when operating at high supply voltages. Copper leadframe construction used in the OPA166x series op amps improves heat dissipation compared to conventional materials. Circuit board layout can also help minimize junction temperature rise. Wide copper traces help dissipate the heat by acting as an additional heat sink. Temperature rise can be further minimized by soldering the devices to the circuit board rather than using a socket.

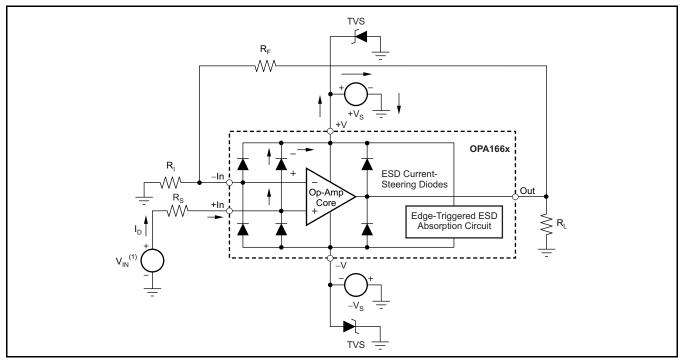

#### **ELECTRICAL OVERSTRESS**

Designers often ask questions about the capability of an operational amplifier to withstand electrical overstress. These questions tend to focus on the device inputs, but may involve the supply voltage pins or even the output pin. Each of these different pin functions have electrical stress limits determined by the voltage breakdown characteristics of the particular semiconductor fabrication process and specific circuits connected to the pin. Additionally, internal electrostatic discharge (ESD) protection is built into these circuits to protect them from accidental ESD events both before and during product assembly.

It is helpful to have a good understanding of this basic ESD circuitry and its relevance to an electrical overstress event. Figure 48 illustrates the ESD circuits contained in the OPA166x (indicated by the dashed line area). The ESD protection circuitry involves several current-steering diodes connected from the input and output pins and routed back to the internal power-supply lines, where they meet at an absorption device internal to the operational amplifier. This protection circuitry is intended to remain inactive during normal circuit operation.

An ESD event produces a short duration, high-voltage pulse that is transformed into a short duration, high-current pulse as it discharges through a semiconductor device. The ESD protection circuits are designed to provide a current path around the operational amplifier core to prevent it from being damaged. The energy absorbed by the protection circuitry is then dissipated as heat.

When an ESD voltage develops across two or more of the amplifier device pins, current flows through one or more of the steering diodes. Depending on the path that the current takes, the absorption device may activate. The absorption device internal to the OPA166x triggers when a fast ESD voltage pulse is impressed across the supply pins. Once triggered, it quickly activates, clamping the ESD pulse to a safe voltage level.

When the operational amplifier connects into a circuit such as that illustrated in Figure 48, the ESD protection components are intended to remain inactive and not become involved in the application circuit operation. However, circumstances may arise where an applied voltage exceeds the operating voltage range of a given pin. Should this condition occur, there is a risk that some of the internal ESD protection circuits may be biased on, and conduct current. Any such current flow occurs through steering diode paths and rarely involves the absorption device.

Figure 48 depicts a specific example where the input voltage,  $V_{IN}$ , exceeds the positive supply voltage  $(+V_S)$  by 500 mV or more. Much of what happens in the circuit depends on the supply characteristics. If  $+V_S$  can sink the current, one of the upper input steering diodes conducts and directs current to  $+V_S$ . Excessively high current levels can flow with increasingly higher  $V_{IN}$ . As a result, the datasheet specifications recommend that applications limit the input current to 10 mA.

If the supply is not capable of sinking the current,  $V_{IN}$  may begin sourcing current to the operational amplifier, and then take over as the source of positive supply voltage. The danger in this case is that the voltage can rise to levels that exceed the operational amplifier absolute maximum ratings. In extreme but rare cases, the absorption device triggers on while  $+V_{S}$  and  $-V_{S}$  are applied. If this event happens, a direct current path is established between the  $+V_{S}$  and  $-V_{S}$  supplies. The power dissipation of the absorption device is quickly exceeded, and the extreme internal heating destroys the operational amplifier.

Another common question involves what happens to the amplifier if an input signal is applied to the input while the power supplies  $+V_S$  and/or  $-V_S$  are at 0 V. Again, it depends on the supply characteristic while at 0 V, or at a level below the input signal amplitude. If the supplies appear as high impedance, then the operational amplifier supply current may be supplied by the input source via the current steering diodes. This state is not a normal bias condition; the amplifier most likely will not operate normally. If the supplies are low impedance, then the current through the steering diodes can become quite high. The current level depends on the ability of the input source to deliver current, and any resistance in the input path.

SBOS489 – DECEMBER 2011 www.ti.com

TEXAS INSTRUMENTS

If there is an uncertainty about the ability of the supply to absorb this current, external zener diodes may be added to the supply pins as shown in Figure 48.

The zener voltage must be selected such that the diode does not turn on during normal operation. However, its zener voltage should be low enough so that the zener diode conducts if the supply pin begins to rise above the safe operating supply voltage level.

(1)  $V_{IN} = +V_S + 500$ mV.

Figure 48. Equivalent Internal ESD Circuitry and Its Relation to a Typical Circuit Application (Single Channel Shown)

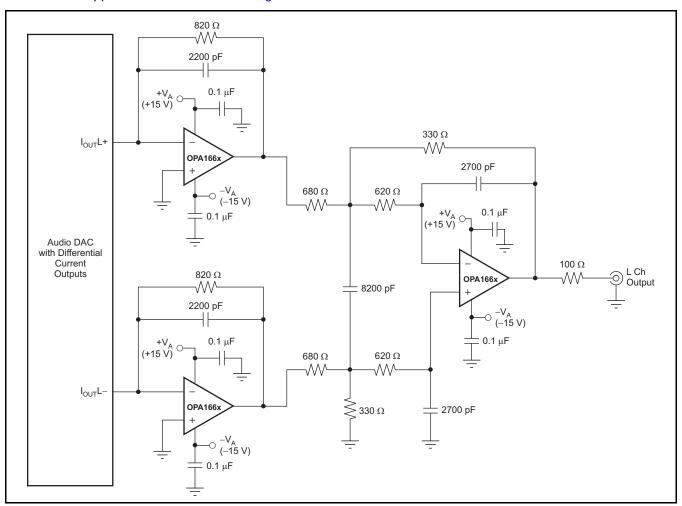

#### **APPLICATION CIRCUIT**

An additional application idea is shown in Figure 49.

Figure 49. Audio DAC I/V Converter and Output Filter

www.ti.com 11-Feb-2023

#### PACKAGING INFORMATION

| Orderable Device | Status | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan     | Lead finish/<br>Ball material | MSL Peak Temp       | Op Temp (°C) | Device Marking (4/5) | Samples |

|------------------|--------|--------------|--------------------|------|----------------|--------------|-------------------------------|---------------------|--------------|----------------------|---------|

| OPA1662AID       | ACTIVE | SOIC         | D                  | 8    | 75             | RoHS & Green | NIPDAU                        | Level-2-260C-1 YEAR | -40 to 85    | OP1662               | Samples |

| OPA1662AIDGK     | ACTIVE | VSSOP        | DGK                | 8    | 80             | RoHS & Green | NIPDAUAG                      | Level-1-260C-UNLIM  | -40 to 85    | OUQI                 | Samples |

| OPA1662AIDGKR    | ACTIVE | VSSOP        | DGK                | 8    | 2500           | RoHS & Green | NIPDAUAG   SN                 | Level-1-260C-UNLIM  | -40 to 85    | OUQI                 | Samples |

| OPA1662AIDR      | ACTIVE | SOIC         | D                  | 8    | 2500           | RoHS & Green | NIPDAU                        | Level-2-260C-1 YEAR | -40 to 85    | OP1662               | Samples |

| OPA1664AID       | ACTIVE | SOIC         | D                  | 14   | 50             | RoHS & Green | NIPDAU                        | Level-2-260C-1 YEAR | -40 to 85    | OPA1664              | Samples |

| OPA1664AIDR      | ACTIVE | SOIC         | D                  | 14   | 2500           | RoHS & Green | NIPDAU                        | Level-2-260C-1 YEAR | -40 to 85    | OPA1664              | Samples |

| OPA1664AIPW      | ACTIVE | TSSOP        | PW                 | 14   | 90             | RoHS & Green | NIPDAU                        | Level-2-260C-1 YEAR | -40 to 85    | OPA1664              | Samples |

| OPA1664AIPWR     | ACTIVE | TSSOP        | PW                 | 14   | 2000           | RoHS & Green | NIPDAU                        | Level-2-260C-1 YEAR | -40 to 85    | OPA1664              | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

**Green:** TI defines "Green" to mean the content of Chlorine (Cl) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

<sup>(5)</sup> Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

#### **PACKAGE OPTION ADDENDUM**

www.ti.com 11-Feb-2023

(6) Lead finish/Ball material - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

#### OTHER QUALIFIED VERSIONS OF OPA1662:

Automotive : OPA1662-Q1

NOTE: Qualified Version Definitions:

Automotive - Q100 devices qualified for high-reliability automotive applications targeting zero defects

#### **PACKAGE MATERIALS INFORMATION**

www.ti.com 3-Jun-2022

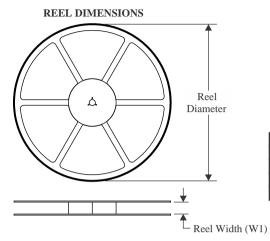

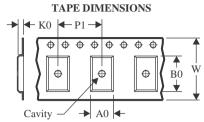

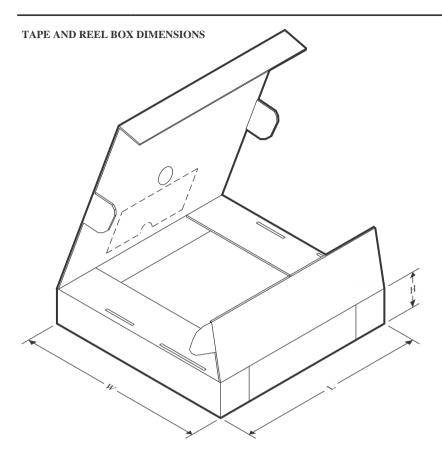

#### TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

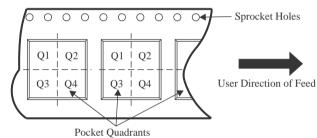

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device        | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|---------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| OPA1662AIDGKR | VSSOP           | DGK                | 8  | 2500 | 330.0                    | 12.4                     | 5.3        | 3.4        | 1.4        | 8.0        | 12.0      | Q1               |

| OPA1662AIDR   | SOIC            | D                  | 8  | 2500 | 330.0                    | 12.4                     | 6.4        | 5.2        | 2.1        | 8.0        | 12.0      | Q1               |

| OPA1664AIDR   | SOIC            | D                  | 14 | 2500 | 330.0                    | 16.4                     | 6.5        | 9.0        | 2.1        | 8.0        | 16.0      | Q1               |

| OPA1664AIPWR  | TSSOP           | PW                 | 14 | 2000 | 330.0                    | 12.4                     | 6.9        | 5.6        | 1.6        | 8.0        | 12.0      | Q1               |

www.ti.com 3-Jun-2022

#### \*All dimensions are nominal

|   | 7 till dillitorioriorio di o riorimidi |                                |     |    |      |             |            |             |

|---|----------------------------------------|--------------------------------|-----|----|------|-------------|------------|-------------|

|   | Device                                 | Device Package Type Package De |     |    |      | Length (mm) | Width (mm) | Height (mm) |

|   | OPA1662AIDGKR                          | VSSOP                          | DGK | 8  | 2500 | 364.0       | 364.0      | 27.0        |

| ı | OPA1662AIDR                            | SOIC                           | D   | 8  | 2500 | 356.0       | 356.0      | 35.0        |

| ı | OPA1664AIDR                            | SOIC                           | D   | 14 | 2500 | 356.0       | 356.0      | 35.0        |

|   | OPA1664AIPWR                           | TSSOP                          | PW  | 14 | 2000 | 356.0       | 356.0      | 35.0        |

#### **PACKAGE MATERIALS INFORMATION**

www.ti.com 3-Jun-2022

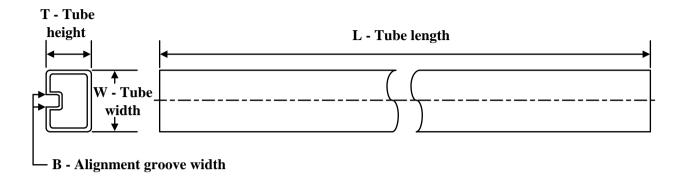

#### **TUBE**

\*All dimensions are nominal

| Device       | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | T (µm) | B (mm) |

|--------------|--------------|--------------|------|-----|--------|--------|--------|--------|

| OPA1662AID   | D            | SOIC         | 8    | 75  | 506.6  | 8      | 3940   | 4.32   |

| OPA1662AIDGK | DGK          | VSSOP        | 8    | 80  | 274    | 6.55   | 500    | 2.88   |

| OPA1664AID   | D            | SOIC         | 14   | 50  | 506.6  | 8      | 3940   | 4.32   |

| OPA1664AIPW  | PW           | TSSOP        | 14   | 90  | 530    | 10.2   | 3600   | 3.5    |

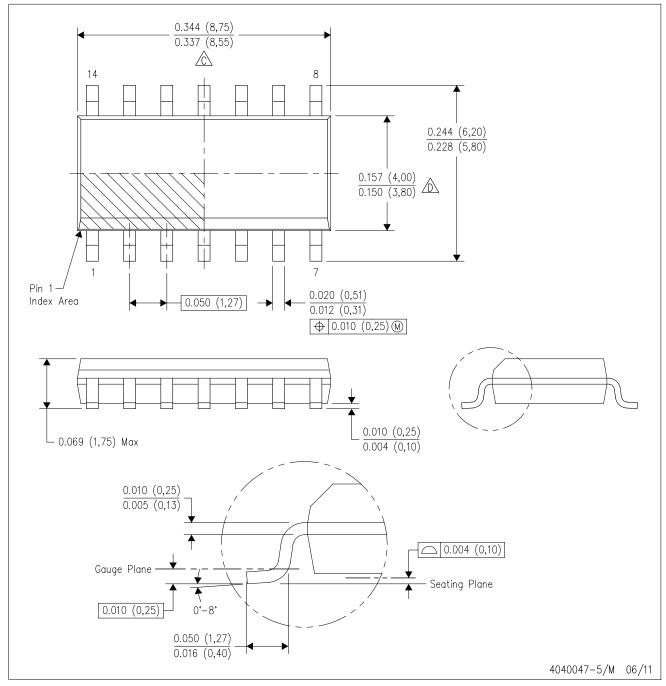

#### D (R-PDSO-G14)

#### PLASTIC SMALL OUTLINE

- A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- Body length does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.006 (0,15) each side.

- Body width does not include interlead flash. Interlead flash shall not exceed 0.017 (0,43) each side.

- E. Reference JEDEC MS-012 variation AB.

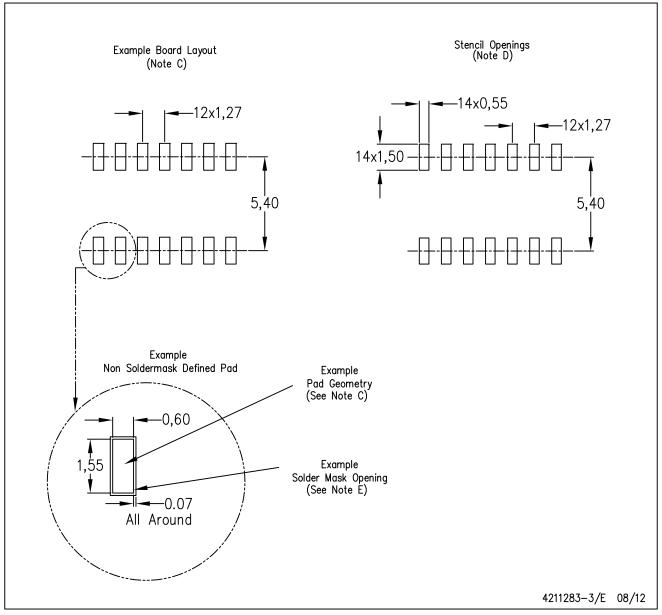

## D (R-PDSO-G14)

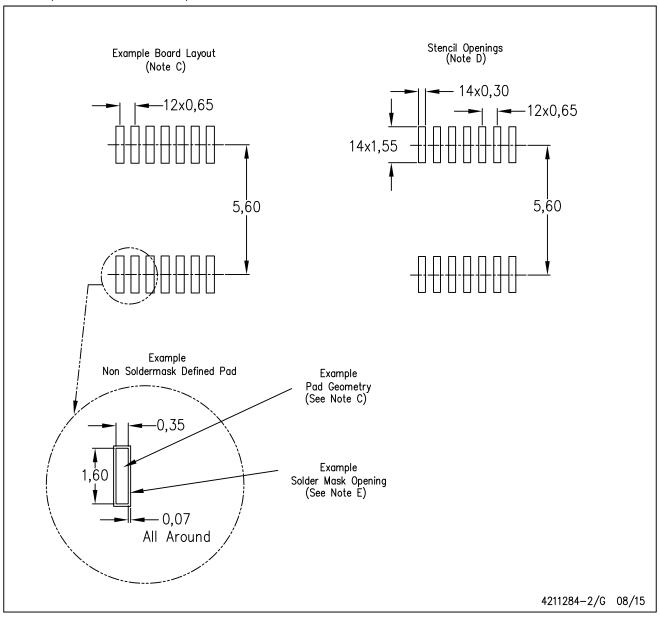

#### PLASTIC SMALL OUTLINE

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Publication IPC-7351 is recommended for alternate designs.

- D. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Refer to IPC-7525 for other stencil recommendations.

- E. Customers should contact their board fabrication site for solder mask tolerances between and around signal pads.

PW (R-PDSO-G14)

#### PLASTIC SMALL OUTLINE

- A. All linear dimensions are in millimeters. Dimensioning and tolerancing per ASME Y14.5M—1994.

- B. This drawing is subject to change without notice.

- Sody length does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0,15 each side.

- Body width does not include interlead flash. Interlead flash shall not exceed 0,25 each side.

- E. Falls within JEDEC MO-153

## PW (R-PDSO-G14)

#### PLASTIC SMALL OUTLINE

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Publication IPC-7351 is recommended for alternate designs.

- D. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Refer to IPC-7525 for other stencil recommendations.

- E. Customers should contact their board fabrication site for solder mask tolerances between and around signal pads.

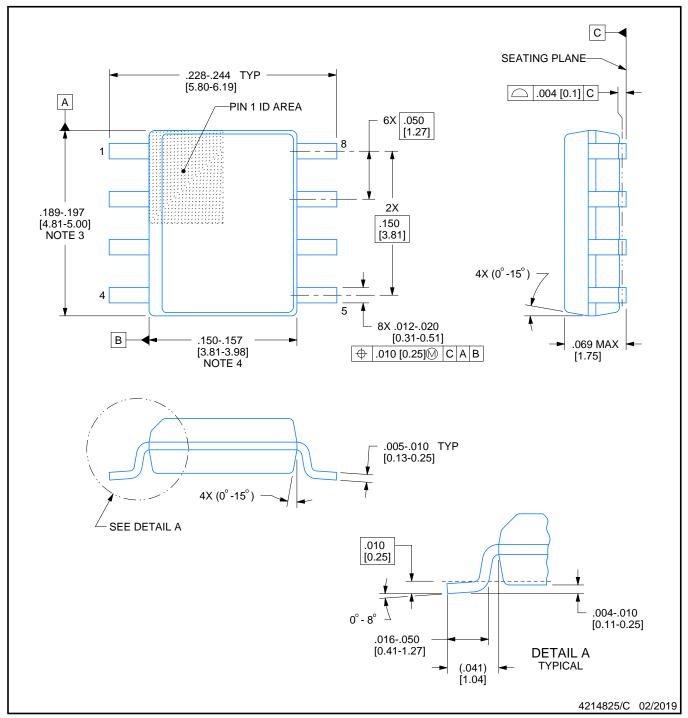

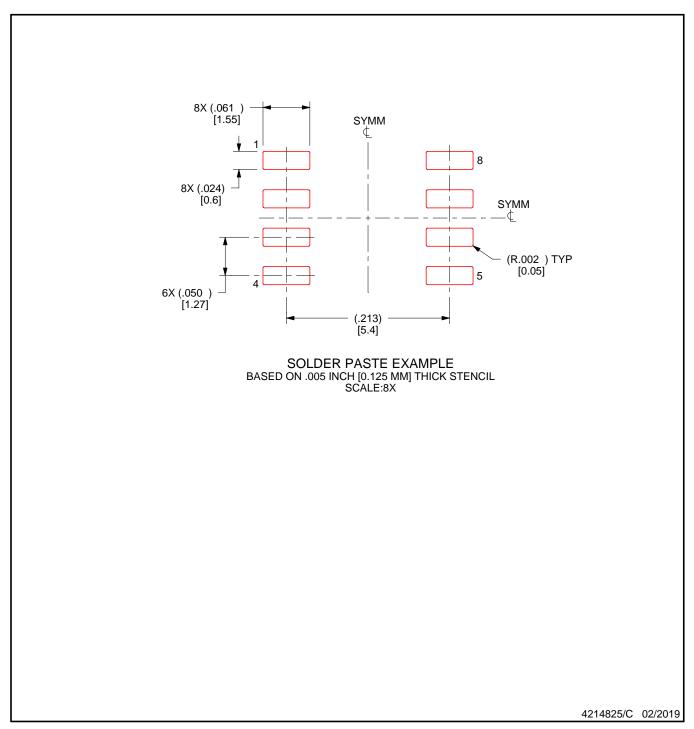

SMALL OUTLINE INTEGRATED CIRCUIT

- 1. Linear dimensions are in inches [millimeters]. Dimensions in parenthesis are for reference only. Controlling dimensions are in inches. Dimensioning and tolerancing per ASME Y14.5M.

- 2. This drawing is subject to change without notice.

- 3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed .006 [0.15] per side.

- 4. This dimension does not include interlead flash.

- 5. Reference JEDEC registration MS-012, variation AA.

SMALL OUTLINE INTEGRATED CIRCUIT

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

SMALL OUTLINE INTEGRATED CIRCUIT

#### NOTES: (continued)

- 8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 9. Board assembly site may have different recommendations for stencil design.

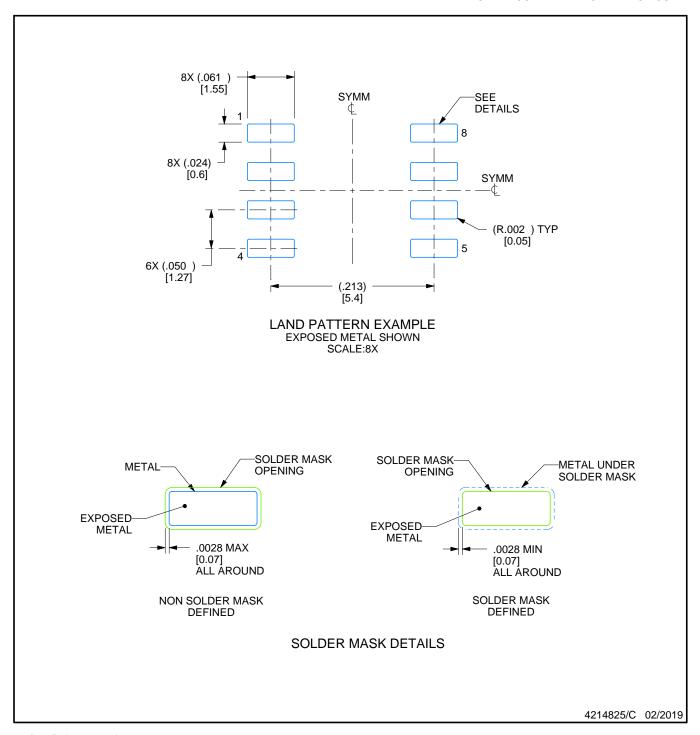

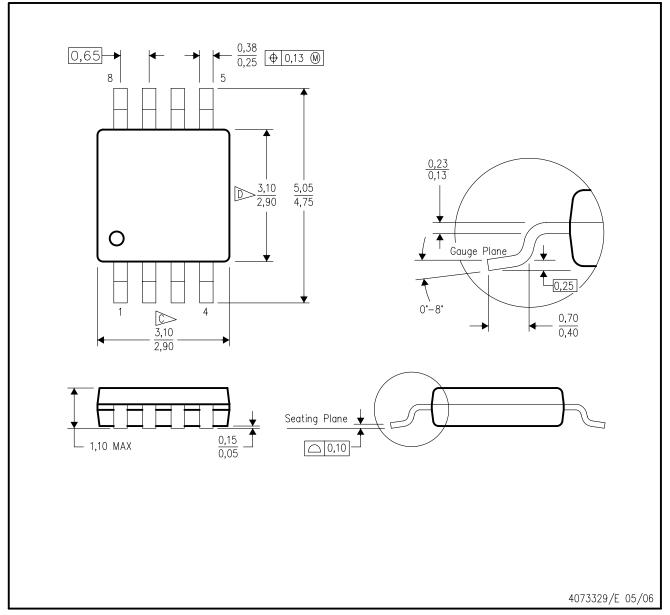

## DGK (S-PDSO-G8)

### PLASTIC SMALL-OUTLINE PACKAGE

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- Body length does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.15 per end.

- Body width does not include interlead flash. Interlead flash shall not exceed 0.50 per side.

- E. Falls within JEDEC MO-187 variation AA, except interlead flash.

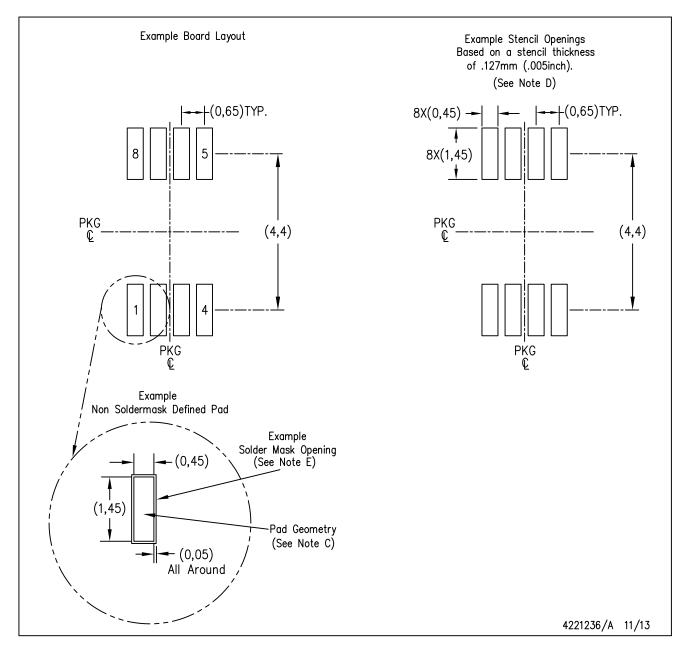

## DGK (S-PDSO-G8)

#### PLASTIC SMALL OUTLINE PACKAGE

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Publication IPC-7351 is recommended for alternate designs.

- D. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Refer to IPC-7525 for other stencil recommendations.

- E. Customers should contact their board fabrication site for solder mask tolerances between and around signal pads.

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2023, Texas Instruments Incorporated