Data sheet acquired from Harris Semiconductor SCHS054C – Revised September 2003

# CD4069UB Types

# **CMOS Hex Inverter**

High-Voltage Types (20-Volt Rating)

CD4069UB types consist of six CMOS inverter circuits. These devices are intended for all general-purpose inverter applications where the medium-power TTL-drive and logic-level-conversion capabilities of circuits such as the CD4009 and CD4049 Hex Inverter/Buffers are not required.

The CD4069UB-Series types are supplied in 14-lead hermetic dual-in-line ceramic packages (F3A suffix), 14-lead dual-in-line plastic packages (E suffix), 14-lead small-outline packages (M, MT, M96, and NSR suffixes), and 14-lead thin shrink small-outline packages (PW and PWR suffixes).

### Features:

- Standardized symmetrical output characteristics

- Medium Speed Operation—tpHL,tpLH=30 ns (typ.) at 10 V

- 100% tested for quiescent current at 20 V

- Maximum input current of 1 μA at 18 V over full package-temperature range; 100 nA at 18 V and 25°C

- Meets all requirements of JEDEC Tentative Standard No. 13B, "Standard Specifications for Description of 'B' Series CMOS Devices"

### Applications:

- Logic inversion

- Pulse shaping

- Oscillators

- High-input-impedance amplifiers

CD4069UB

**FUNCTIONAL DIAGRAM**

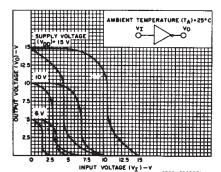

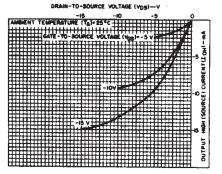

Fig. 1 — Minimum and maximum voltage transfer characteristics.

### RECOMMENDED OPERATING CONDITIONS

MAXIMUM RATINGS, Absolute-Maximum Values:

For maximum reliability, nominal operating conditions should be selected so that operation is always within the following ranges:

| CHARACTERISTIC                                                  | LII  | UNITS |   |  |  |

|-----------------------------------------------------------------|------|-------|---|--|--|

|                                                                 | Min. | Max.  |   |  |  |

| Supply Voltage Range (For TA=Full Package<br>Temperature Range) | 3    | 18    | V |  |  |

# DC SUPPLY-VOLTAGE RANGE, $(V_{DD})$ Voltages referenced to $V_{SS}$ Terminal) -0.5V to +20V INPUT VOLTAGE RANGE, ALL INPUTS -0.5V to $V_{DD}$ +0.5V DC INPUT CURRENT, ANY ONE INPUT ±10mA POWER DISSIPATION PER PACKAGE $(P_D)$ : For $T_A = -55^{\circ}$ C to +100°C For $T_A = +100^{\circ}$ C to +125°C Derate Linearity at 12mW/°C to 200mW DEVICE DISSIPATION PER OUTPUT TRANSISTOR FOR $T_A = FULL$ PACKAGE-TEMPERATURE RANGE (All Package Types) 100mW OPERATING-TEMPERATURE RANGE $(T_{SL})$ STORAGE TEMPERATURE RANGE $(T_{SL})$ -65°C to +150°C LEAD TEMPERATURE (DURING SOLDERING): At distance 1/16 $\pm$ 1/32 inch (1.59 $\pm$ 0.79mm) from case for 10s max +265°C

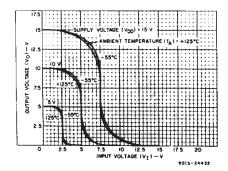

Fig. 2 — Typical voltage transfer characteristics as a function of temperature.

|                         | CONDITIONS                          | LIMITS    |      | UNITS |    |  |  |

|-------------------------|-------------------------------------|-----------|------|-------|----|--|--|

| CHARACTERISTIC          | V <sub>DD</sub>                     |           |      |       |    |  |  |

|                         |                                     | V         | Тур. | Max.  | l  |  |  |

| Propagation Delay Time; |                                     | 5         | 55   | 110   | ns |  |  |

|                         | *=*=                                | 10        | 30   | 60    |    |  |  |

|                         | <sup>t</sup> PLH <sup>, t</sup> PHL | 15        | 25   | 50    |    |  |  |

| Transition Time;        |                                     | 5         | 100  | 200   |    |  |  |

|                         | tTHL, tTLH                          | 10        | 50   | 100   | ns |  |  |

|                         |                                     | 15        | 40   | 80    |    |  |  |

| Input Capacitance;      | c <sub>IN</sub>                     | Any Input | 10   | 15    | pF |  |  |

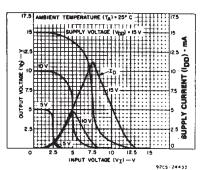

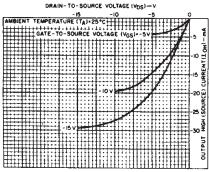

Fig. 3 — Typical current and voltage transfer characteristics.

# CD4069UB Types

### STATIC ELECTRICAL CHARACTERISTICS

| CHARACTER-                                      | CONDITIONS |       |     | LIMITS AT INDICATED TEMPERATURES (°C) |       |              |       |       |                   |      |           |  |  |

|-------------------------------------------------|------------|-------|-----|---------------------------------------|-------|--------------|-------|-------|-------------------|------|-----------|--|--|

| ISTIC                                           | Vo         | VIN   | VDD |                                       |       |              |       | +25   |                   |      | UNITS     |  |  |

|                                                 | (V)        | (V)   | (V) | 55                                    | -40   | +85          | +125  | Min.  | Тур.              | Max. | <u></u>   |  |  |

| Quiescent Device<br>Current,<br>IDD Max.        |            | 0,5   | 5   | 0.25                                  | 0.25  | 7.5          | 7.5   | -     | 0.01              | 0.25 | μΑ        |  |  |

|                                                 |            | 0,10  | 10  | 0.5                                   | 0.5   | 15           | 15    | -     | 0.01              | 0.5  |           |  |  |

|                                                 | -          | 0,15  | 15  | 1                                     | 1     | 30           | 30    |       | 0.01              | 1    |           |  |  |

|                                                 | _          | 0,20  | 20  | 5                                     | 5     | 150          | 150   | _     | 0.02              | 5    |           |  |  |

| Output Low<br>(Sink) Current<br>IOL Min.        | 0.4        | 0,5   | 5   | 0.64                                  | 0.61  | 0.42         | 0.36  | 0.51  | 1                 | -    |           |  |  |

|                                                 | 0.5        | 0,10  | 10  | 1.6                                   | 1.5   | 1.1          | 0.9   | 1.3   | 2.6               |      | mA        |  |  |

|                                                 | 1.5        | 0,15  | 15  | 4.2                                   | 4     | 2.8          | 2.4   | 34    | 6.8               | -    |           |  |  |

| Output High<br>(Source)<br>Current,<br>IOH Min. | 4.6        | 0,5   | 5   | -0.64                                 | -0.61 | -0.42        | -0.36 | -0.51 | -1                |      |           |  |  |

|                                                 | 2.5        | 0,5   | 5   | -2                                    | -1.8  | -1.3         | -1.15 | -1.6  | -3.2              | -    |           |  |  |

|                                                 | 9.5        | 0,10  | 10  | -1.6                                  | -1.5  | -1.1         | -0.9  | -1.3  | -2.6              | _    |           |  |  |

|                                                 | 13.5       | .0,15 | 15  | -4.2                                  | -4    | -2.8         | -2.4  | -3.4  | -6.8              | -    |           |  |  |

| Output Voltage:                                 | _          | 5     | 5   | 0.05                                  |       |              |       | _     | 0                 | 0.05 | V         |  |  |

| Low-Level,<br>VOL Max.                          |            | 10    | 10  | 0.05                                  |       |              |       | _     | -0                | 0.05 |           |  |  |

| AOF Max.                                        | . –        | 15    | 15  | 0.05                                  |       |              |       | 0.    | 0.05              |      |           |  |  |

| Output Voltage:                                 |            | 0     | 5   | 4.95                                  |       |              |       | 4.95  | 5                 | -    | \ \       |  |  |

| High-Level,<br>VOH Min.                         |            | 0     | 10  |                                       | 9     | .95          |       | 9.95  | 10                | -    | $\exists$ |  |  |

|                                                 |            | 0     | 15  |                                       | 14    | .95          |       | 14.95 | 15                | -    |           |  |  |

| Input Low<br>Voltage,<br>VIL Max.               | 4.5        | _     | 5   |                                       |       | T            |       | _     | _                 | 1    |           |  |  |

|                                                 | 9          | _     | 10  |                                       |       | 2            |       |       | _                 | 2    |           |  |  |

|                                                 | 13.5       | _     | 15  |                                       | . 2   | .5           |       | _     | _                 | 2.5  | 7         |  |  |

| Input High<br>Voltage,<br>VIH Min.              | 0.5        | _     | 5   |                                       |       | 4            |       | 4     | -                 |      | · V       |  |  |

|                                                 | 1          |       | 10  | 8 8                                   |       |              |       | -     |                   |      |           |  |  |

|                                                 | 1.5        |       | 15  |                                       | 12    | 2.5 12.5 — — |       |       |                   | -    | .         |  |  |

| Input Current IJN Max.                          |            | 0,18  | 18  | ±0.1                                  | ±0.1  | ±1           | ±1    | _     | ±10 <sup>-5</sup> | ±0.1 | μΑ        |  |  |

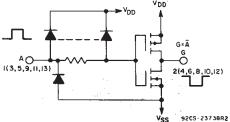

Fig. 6 - Schematic diagram of one of six identical inverters.

Fig. 9 — Minimum output high (source) current characteristics.

Fig. 7 - CD4069UB terminal assignment.

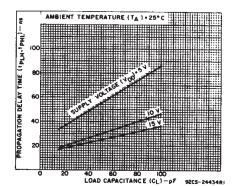

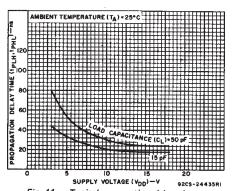

Fig. 10 — Typical propagation delay time vs. load capacitance.

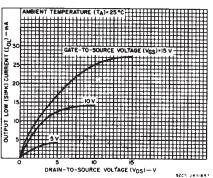

Fig. 4 – Typical output low (sink) current characteristics.

Fig. 5 = Minimum output low (sink) current characteristics.

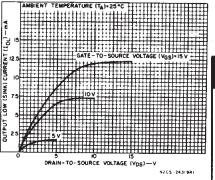

Fig. 8 — Typical output high (source) current characteristics.

Fig. 11 — Typical propagation delay time vs. supply voltage.

## CD4069UB Types

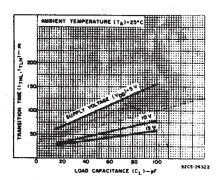

Fig. 12 - Typical transition time vs. load capacitance.

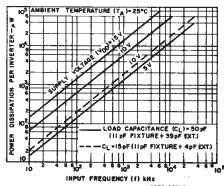

Fig. 13 — Typical dynamic power dissipation vs. frequency.

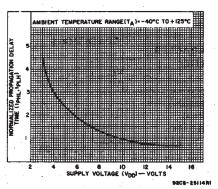

Fig. 14 - Variation of normalized propagation delay time ( $t_{PHL}$  and  $t_{PLH}$ ) with supply voltage.

Fig. 15 - Quiescent device current test circuit.

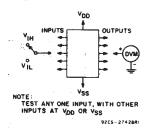

Fig. 16 - Noise immunity test circuit.

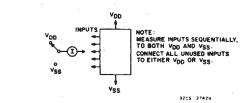

Fig. 17 - Input leakage current test circuit. **APPLICATIONS**

-- 90% -10% ADD F ----10%<sub>0</sub> 92CM~24443Rt

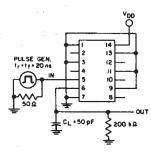

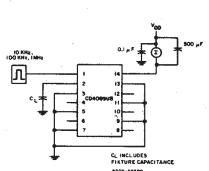

Fig. 18 - Dynamic electrical characteristics test circuit and waveforms.

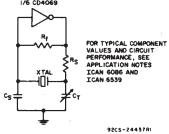

Fig. 19 - Typical crystal oscillator circuit.

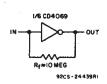

Fig. 20 - High-input impedance amplifier.

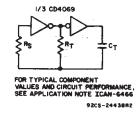

Fig. 21 - Typical RC oscillator circuit.

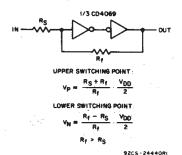

Fig. 22 - Input pulse shaping circuit (Schmitt trigger).

Fig. 23 - Dynamic power dissipation test circuit.

Dimensions and pad layout for CD4069UBH.

Dimensions in parentheses are in millimeters and are derived from the basic inch dimensions as indicated. Grid graduations are in mils ( $10^{-3}$  inch).