# INTEGRATED CIRCUITS

# DATA SHEET

# TDA8730 PLL FM demodulator for DBS signals

Preliminary specification

File under Integrated Circuits, IC02

March 1991

**TDA8730**

#### **FEATURES**

- · Broadband IF amplifier

- PLL demodulator, consisting of:

- a multiplier

- a voltage controlled oscillator

- a loop amplifier

- · AGC detector and DC amplifier

- LOW impedance video and data output

- Power supply voltage stabilizer

# **GENERAL DESCRIPTION**

The TDA8730 is a sensitive PLL demodulator for the second IF and direct broadcasting satellite (DBS) receivers. It provides AGC output and threshold adjustment for optimal signal level at the input of the demodulator.

#### **QUICK REFERENCE DATA**

| SYMBOL           | PARAMETER                                          | CONDITIONS | MIN. | TYP. | MAX.     | UNIT |

|------------------|----------------------------------------------------|------------|------|------|----------|------|

| $V_{DD}$         | supply voltage                                     |            | _    | 9    | _        | V    |

| I <sub>DD</sub>  | supply current                                     |            | _    | 75   | _        | mA   |

| VI               | input voltage level                                |            | _    | 70   | _        | dΒμV |

| f <sub>osc</sub> | minimum oscillator frequency                       |            | _    | 130  | _        | MHz  |

| f <sub>osc</sub> | maximum oscillator frequency                       |            | _    | 720  | _        | MHz  |

| Vo               | video output signal amplitude (peak-to-peak value) | note 1     | _    | 1.1  | _        | V    |

| V <sub>AGC</sub> | AGC output voltage                                 |            | 1.8  | _    | $V_{DD}$ | V    |

# Note

1.  $\Delta f = 13.5 \text{ MHz}$  (peak-to-peak value)

# ORDERING AND PACKAGE INFORMATION

| EXTENDED TYPE | PACKAGE |              |          |                        |  |  |  |

|---------------|---------|--------------|----------|------------------------|--|--|--|

| NUMBER        | PINS    | PIN POSITION | MATERIAL | CODE                   |  |  |  |

| TDA8730       | 16      | DIL          | plastic  | SOT38GE <sup>(1)</sup> |  |  |  |

# Note

1. SOT38-1; 1996 December 4.

# PLL FM demodulator for DBS signals

TDA8730

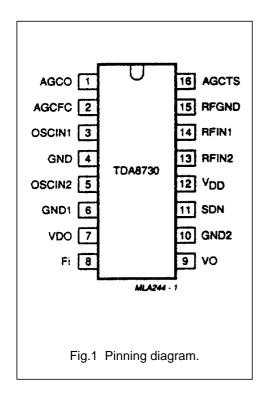

# **PINNING**

| SYMBOL   | PIN | DESCRIPTION                     |

|----------|-----|---------------------------------|

| AGCO     | 1   | AGC output                      |

| AGCFC    | 2   | AGC frequency compensation      |

| OSCIN1   | 3   | oscillator input 1              |

| GND      | 4   | GND                             |

| OSCIN2   | 5   | oscillator input 2              |

| GND1     | 6   | ground 1                        |

| VDO      | 7   | variable capacitor drive output |

| FI       | 8   | feedback input                  |

| VO       | 9   | video output                    |

| GND2     | 10  | ground 2                        |

| SDN      | 11  | stabilizer decoupling node      |

| $V_{DD}$ | 12  | supply voltage +9 V             |

| RFIN2    | 13  | RF input 2                      |

| RFIN1    | 14  | RF input 1                      |

| RFGND    | 15  | RF ground                       |

| AGCTS    | 16  | AGC threshold setting           |

# **APPLICATIONS**

Direct broadcasting satellite (DBS) receivers.

TDA8730

# PLL FM demodulator for DBS signals

TDA8730

# **FUNCTIONAL DESCRIPTION**

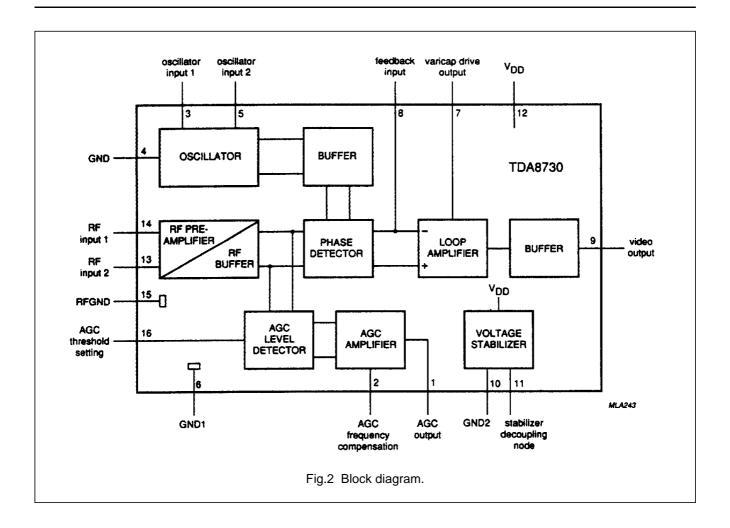

The TDA8730 is a PLL FM demodulator intended for use in satellite tuners. It can demodulate frequency deviations ranging from 13.5 MHz<sub>(p-p)</sub> (DBS services) up to 25 MHz(p-p) (FSS services) and offers a high demodulation linearity. The circuit is optimized for operation at 479.5 MHz (the European IF for satellite tuners) and can handle the various broadcasting standards that are in use (including MAC). Due to the PLL principle, demodulation noise threshold extension is possible. The high sensitivity of the balanced IF input reduces the additional gain, required in the tuner. An on chip AGC circuit delivers a gain control signal for use by the tuner IF amplifier, and a voltage regulator makes the circuit insensitive supply voltage changes.

#### **LIMITING VALUES**

In accordance with the Absolute Maximum System (IEC 134)

| SYMBOL                 | PARAMETER                         | MIN. | MAX.     | UNIT |

|------------------------|-----------------------------------|------|----------|------|

| $V_{DD}$               | supply voltage                    | -0.3 | 11       | V    |

| I <sub>DD</sub>        | input voltage                     | -0.3 | $V_{DD}$ | V    |

| I <sub>O(source)</sub> | output source current             | _    | 10       | mA   |

| $V_{AGC}$              | AGC output voltage                | _    | 11       | V    |

| t <sub>sc</sub>        | max short circuit time of outputs | 10   | _        | s    |

| V <sub>AGC(adj)</sub>  | AGC threshold adjustment voltage  | -0.3 | $V_{DD}$ | V    |

| T <sub>stg</sub>       | storage temperature               | -55  | 150      | °C   |

| T <sub>j</sub>         | junction temperature              | _    | 150      | °C   |

| T <sub>amb</sub>       | operating ambient temperature     | -25  | 85       | °C   |

# THERMAL RESISTANCE

| SYMBOL              | PARAMETER                            | TYP. | MAX. | UNIT |

|---------------------|--------------------------------------|------|------|------|

| R <sub>th i-a</sub> | from-junction-to-ambient in free air | 55   | _    | K/W  |

# PLL FM demodulator for DBS signals

TDA8730

# **CHARACTERISTICS**

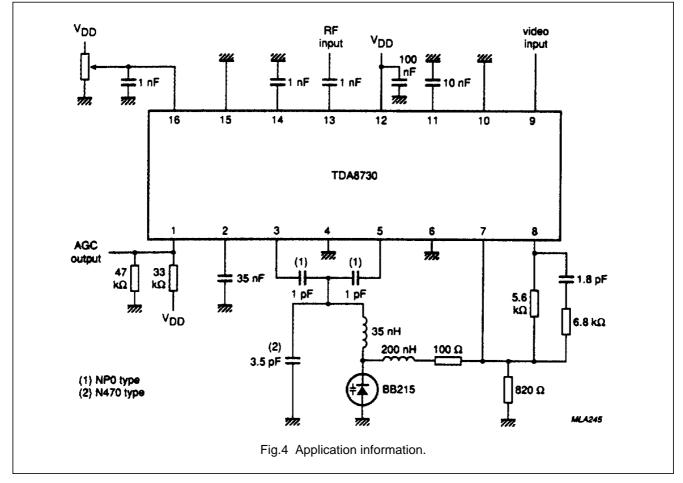

$V_{DD} = 9 \text{ V; } T_{amb} = 25 \text{ }^{\circ}\text{C; } f = 480 \text{ MHz; Input level } 70 \text{ } dB\mu\text{V; measured in circuit of Fig.4 unless otherwise specified.}$

| SYMBOL            | PARAMETER                                                                                                  | CONDITIONS                             | MIN.                 | TYP. | MAX      | UNIT   |

|-------------------|------------------------------------------------------------------------------------------------------------|----------------------------------------|----------------------|------|----------|--------|

| Supply            |                                                                                                            |                                        | -                    |      |          |        |

| $V_{DD}$          | supply voltage                                                                                             | V <sub>pin 12</sub> to pin 10 or pin15 | 8.1                  | 9.0  | 9.9      | V      |

| I <sub>DD</sub>   | supply current                                                                                             | I <sub>pin 12</sub> ; note 1           | _                    | 75   | 90       | mA     |

| Frequency         | demodulator                                                                                                |                                        | •                    |      |          |        |

| f <sub>osc</sub>  | minimum oscillator frequency                                                                               | _                                      | _                    | 130  | _        | MHz    |

| f <sub>osc</sub>  | maximum oscillator frequency                                                                               | _                                      | _                    | 720  | _        | MHz    |

| Vi                | operating input level                                                                                      | pin 13; note 2                         | _                    | 70   | 74       | dΒμV   |

|                   | input reflection coefficient  \$11                                                                         |                                        |                      |      |          |        |

| S11               | unbalanced; pin 14 decoupled (50 $\Omega$ reference)                                                       | pin 13; note 3                         | _                    | 0.07 | _        |        |

|                   | balanced; 100 Ω reference                                                                                  | pin 13 to pin 14                       | _                    | 0.11 | _        |        |

| Kd                | phase detector constant                                                                                    | (level at pin 13 is 70 dBμV)           | _                    | 0.45 | _        | V/rad. |

| Ko                | VCO constant                                                                                               |                                        | _                    | 12   | _        | MHz/V  |

| Ao                | open loop gain of loop amplifier                                                                           | pin 7 to pin 8                         | _                    | 40   | _        | dB     |

| f-3 dB            | open loop bandwidth of loop amplifier                                                                      |                                        | _                    | 2.8  | _        | MHz    |

| Z <sub>in</sub>   | input impedance of feedback input                                                                          | pin 8                                  | _                    | 930  | _        | Ω      |

| Z <sub>out</sub>  | output impedance of loop amplifier                                                                         | pin 7                                  | _                    | 30   | 50       | Ω      |

| le                | VCO linearity error over $\Delta f = \pm 10 \text{ MHz}$                                                   | note 4                                 | _                    | 1    | _        | %      |

|                   | shift of DC level at video output for $\Delta V_{DD} = \pm 10\%$ with unmodulated 480 MHz input signal     | pin 9                                  | _                    | _    | ±50      | mV     |

|                   | drift of DC level at video output for T <sub>amb</sub> = 25 to 50 °C with unmodulated 480 MHz input signal | pin 9                                  | _                    | _    | +50      | mV     |

| V <sub>VCO</sub>  | VCO capture range                                                                                          |                                        | ±14                  | _    | _        | MHz    |

| G <sub>d</sub>    | differential gain                                                                                          | note 5                                 | _                    | -    | ±4       | %      |

| φ <sub>d</sub>    | differential phase                                                                                         | note 5                                 | _                    | _    | ±2       | deg.   |

| MOD               | intermodulation                                                                                            | note 6                                 | _                    | -70  | _        | dB     |

| AGC               |                                                                                                            |                                        | 1                    | '    | •        |        |

| V <sub>IAGC</sub> | AGC threshold (IAGC = 0 mA) as a function of voltage applied to pin 16                                     | pin 13                                 |                      |      |          |        |

|                   | $V_{\text{pin}16} = 0.8 \text{ V}$                                                                         | _                                      | _                    | _    | 67       | dBμV   |

|                   | $V_{pin 16} = 9.0 \text{ V}$                                                                               | note 7                                 | 73                   | -    | -        | dBμV   |

|                   | AGC steepness                                                                                              | pin 1; note 8                          | _                    | 18   | -        | mA/dB  |

|                   | AGC output saturation voltage HIGH at I = -0.2 mA                                                          | V <sub>pin 1</sub> to pin 10 or pin 15 | V <sub>DD</sub> -0.5 | _    | $V_{DD}$ | V      |

|                   | AGC output saturation voltage LOW at I = 0.2 mA                                                            |                                        | _                    | 1.8  | 2.3      | V      |

# PLL FM demodulator for DBS signals

TDA8730

| SYMBOL             | PARAMETER                                            | CONDITIONS                           | MIN. | TYP. | MAX | UNIT |  |  |

|--------------------|------------------------------------------------------|--------------------------------------|------|------|-----|------|--|--|

| Video outp         | out                                                  |                                      |      |      |     |      |  |  |

| Vo                 | video output signal amplitude<br>(Δf = 13.5 MHz p-p) | pin 9 to pin 10 or pin 15            | _    | 1.1  | _   | V    |  |  |

| V <sub>O(DC)</sub> | DC level of video output                             | pin 9 to pin 10 or pin 15;<br>note 9 | 3.1  | 3.5  | 3.9 | V    |  |  |

| Z <sub>O</sub>     | output impedance                                     | pin 9                                | _    | 30   | 50  | Ω    |  |  |

| Z <sub>L</sub>     | AC load impedance                                    | pin 9; note 10                       | 600  | Ī-   | -   | Ω    |  |  |

| Voltage re         | Voltage regulator                                    |                                      |      |      |     |      |  |  |

| V <sub>ref</sub>   | reference voltage for  I <sub>load</sub>   ≤ 1 mA    | pin 11; note 11                      | _    | 7    | -   | V    |  |  |

| V <sub>reg</sub>   | line regulation 8.1 V ≤ VIN ≤ 9.9 V                  | pin 11                               | _    | 70   | -   | mV   |  |  |

| I <sub>load</sub>  | allowable load current                               | pin 11                               | -1   | _    | 0   | mA   |  |  |

#### **Notes**

- 1. The supply current is the consumption of the circuit only.

- The current consumption of this application is given by the addition of the supply current of the circuit plus the current consumption of external components in the application given. In this event (Fig.4) the typical current is 80 mA.

- 2. The circuit of Fig.4 is designed for an input level of 70 dB $\mu$ V. The maximum allowable input level for PLL design is 74 dB $\mu$ V. However, for levels other than 70 dB $\mu$ V the optimum loop filter values will be different from those given in Fig.4.

- 3. In the application circuit of Fig.4 the RF input is asymmetrically driven. In order to reduce the influence of oscillator signal coupling to the RF inputs, it is recommended to use a symmetrical drive at both inputs.

- 4. The linearity is specified as the maximum difference between the slope df/dV at the channel centre frequency (480 MHz) and the slope at 480 MHz  $\pm$  10 MHz.

- 5. Measurements with test signals in accordance with CCIR Rec. 473-3; Fm signal with DBS parameters: pre-and de-emphasis in accordance with CCIR Rec. 405-1, 625 lines PAL TV system. Modulator sensitive 13.5 MHz/V at pre-emphasis cross over frequency 1 V(p-p) video signal at pre-emphasis filter input.

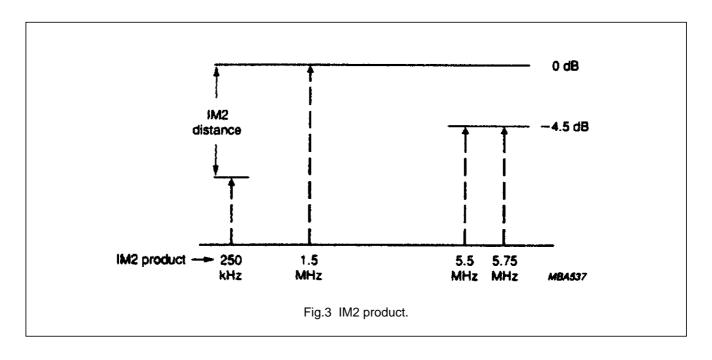

- 6. For the intermodulation measurement, an FM test signal is applied having the following modulating components: 1.5 MHz reference sinewave with a deviation of 9.45 MHz(p-p), 5.5 and 5.75 MHz sinewaves with deviation 5.6 MHz(p-p) (so 4.5 dB below the reference, see Fig.3). At the demodulator output the 2nd order intermodulation is defined according to Fig.3. The video output is loaded with 500 Ω resistor + DC blocking capacitor.

- 7. The voltage applied at pin 16 is allowed to be higher than the minimum supply voltage (8.1 V).

- 8. The voltage at the AGC output (pin 1) decreases when the RF input level at pin 13 increases above the adjusted AGC threshold.

- 9. The DC level at the video output decreases when the RF input frequency increases.

The DC level at the video output (pin 9) is measured with the VCO switched off because when the oscillator is operating, the DC level is dependent on the application (oscillator into the input).

- 10. The load impedance must have at least the minimum value for a frequency range from DC to the bandwidth of the i.f. filter (usually 27 MHz) since wide-band noise components will also appear at the video output.

- 11. It is possible to use the regulator output voltage (pin 11). The maximum current allowed is 1 mA. Possible application as voltage reference source for AFC circuit.

# TDA8730

TDA8730

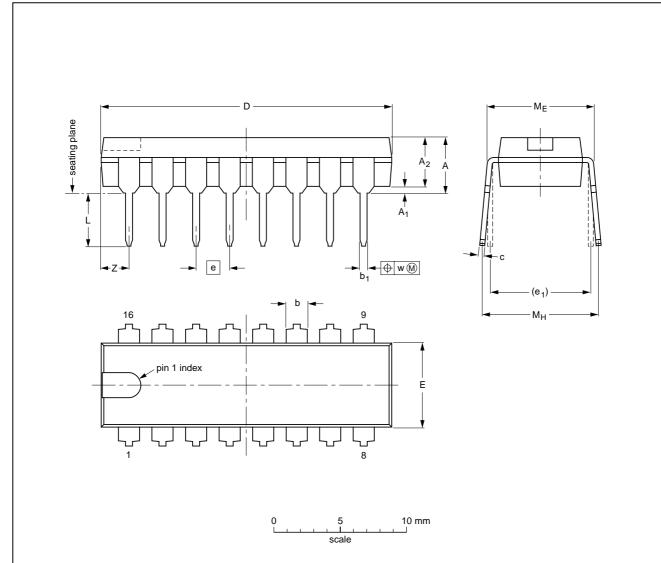

# **PACKAGE OUTLINE**

DIP16: plastic dual in-line package; 16 leads (300 mil); long body

SOT38-1

# DIMENSIONS (inch dimensions are derived from the original mm dimensions)

| UNIT   | A<br>max. | A <sub>1</sub><br>min. | A <sub>2</sub><br>max. | b              | b <sub>1</sub> | С              | D <sup>(1)</sup> | E <sup>(1)</sup> | е    | e <sub>1</sub> | L            | ME           | M <sub>H</sub> | w     | Z <sup>(1)</sup><br>max. |

|--------|-----------|------------------------|------------------------|----------------|----------------|----------------|------------------|------------------|------|----------------|--------------|--------------|----------------|-------|--------------------------|

| mm     | 4.7       | 0.51                   | 3.7                    | 1.40<br>1.14   | 0.53<br>0.38   | 0.32<br>0.23   | 21.8<br>21.4     | 6.48<br>6.20     | 2.54 | 7.62           | 3.9<br>3.4   | 8.25<br>7.80 | 9.5<br>8.3     | 0.254 | 2.2                      |

| inches | 0.19      | 0.020                  | 0.15                   | 0.055<br>0.045 | 0.021<br>0.015 | 0.013<br>0.009 | 0.86<br>0.84     | 0.26<br>0.24     | 0.10 | 0.30           | 0.15<br>0.13 | 0.32<br>0.31 | 0.37<br>0.33   | 0.01  | 0.087                    |

#### Note

1. Plastic or metal protrusions of 0.25 mm maximum per side are not included.

| OUTLINE |        | REFER    | ENCES | EUROPEAN   | ISSUE DATE                      |

|---------|--------|----------|-------|------------|---------------------------------|

| VERSION | IEC    | JEDEC    | EIAJ  | PROJECTION | ISSUE DATE                      |

| SOT38-1 | 050G09 | MO-001AE |       |            | <del>92-10-02</del><br>95-01-19 |

# PLL FM demodulator for DBS signals

TDA8730

#### **SOLDERING**

#### Introduction

There is no soldering method that is ideal for all IC packages. Wave soldering is often preferred when through-hole and surface mounted components are mixed on one printed-circuit board. However, wave soldering is not always suitable for surface mounted ICs, or for printed-circuits with high population densities. In these situations reflow soldering is often used

This text gives a very brief insight to a complex technology. A more in-depth account of soldering ICs can be found in our "IC Package Databook" (order code 9398 652 90011).

#### Soldering by dipping or by wave

The maximum permissible temperature of the solder is 260 °C; solder at this temperature must not be in contact with the joint for more than 5 seconds. The total contact time of successive solder waves must not exceed 5 seconds.

The device may be mounted up to the seating plane, but the temperature of the plastic body must not exceed the specified maximum storage temperature (T<sub>stg max</sub>). If the printed-circuit board has been pre-heated, forced cooling may be necessary immediately after soldering to keep the temperature within the permissible limit.

# Repairing soldered joints

Apply a low voltage soldering iron (less than 24 V) to the lead(s) of the package, below the seating plane or not more than 2 mm above it. If the temperature of the soldering iron bit is less than 300 °C it may remain in contact for up to 10 seconds. If the bit temperature is between 300 and 400 °C, contact may be up to 5 seconds.

#### **DEFINITIONS**

| Data sheet status         |                                                                                       |

|---------------------------|---------------------------------------------------------------------------------------|

| Objective specification   | This data sheet contains target or goal specifications for product development.       |

| Preliminary specification | This data sheet contains preliminary data; supplementary data may be published later. |

| Product specification     | This data sheet contains final product specifications.                                |

| Limiting values           |                                                                                       |

# Limiting values

Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of the specification is not implied. Exposure to limiting values for extended periods may affect device reliability.

# **Application information**

Where application information is given, it is advisory and does not form part of the specification.

#### LIFE SUPPORT APPLICATIONS

These products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Philips customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips for any damages resulting from such improper use or sale.